厦大&中兴团队!突破 8 英寸晶圆级CMOS芯片微通道液冷

来源 | IEEE

链接 | https://doi.org/10.1109/ICEPT67137.2025.11157006

01

背景介绍

在人工智能(AI)、高性能计算(HPC)技术爆发式发展的当下,我们对计算芯片的性能需求正以肉眼可见的速度攀升。为了满足这种需求,芯片产业不断突破技术边界 —— 从更先进的制程节点,到 2.5D/3D 集成等创新封装技术,每一步升级都在推动芯片性能迈上新台阶。但随之而来的,是一个愈发严峻的 “副作用”:封装内部的功率密度急剧升高,芯片的热管理挑战被推向了前所未有的高度。

以行业标杆为例,英伟达基于晶圆级芯片 - 基板局部互连(CoWoS-L)技术的 Blackwell 图形处理器(GPU),其热设计功率(TDP)已突破 1000 瓦。这意味着芯片在高速运算时会产生海量热量,若不能及时有效散出,不仅会导致性能 “降频”,还可能直接影响芯片的稳定性与使用寿命。传统的封装外散热方案(如风冷、外置液冷)已逐渐力不从心,如何让散热系统更贴近热源、降低热阻,成为解决高功率芯片散热问题的核心方向。

事实上,“微通道冷却” 并非全新概念。早在 1981 年,Tuckerman 和 Pease 就提出了这一技术,它通过在芯片附近构建微小通道,让冷却液直接与热源接触,理论上具备远超传统方案的散热效率,因此被视为芯片热管理的潜在 “救星”。近年来,行业也在不断推进其落地探索:2021 年,台积电(TSMC)就发布了针对超高功率 3D-IC 的高效热管理研究,通过低热阻键合技术将微通道冷却器与芯片集成,实现了液冷功能,其氧化硅(SiOₓ)键合界面的热阻低至 1.5 K・mm²/W。这项研究不仅再次验证了微通道冷却对高功率芯片的有效性,也为先进封装架构下的微通道与 IC 芯片集成提供了可行思路。

然而,当前的微通道冷却研究仍存在一个关键 “短板”:绝大多数成果停留在实验室阶段 —— 研究重点集中在微通道的新颖设计、小批量样品制作与热性能表征上,却鲜少关注 “工业兼容性” 问题。也就是说,现有技术方案难以适配倒装芯片(FC)、2.5D/3D 集成等先进封装的工业化量产流程。这种 “实验室与工厂脱节” 的现状,严重阻碍了微通道冷却技术的成熟,也延缓了它在实际高功率芯片产品中的应用。

02

成果掠影

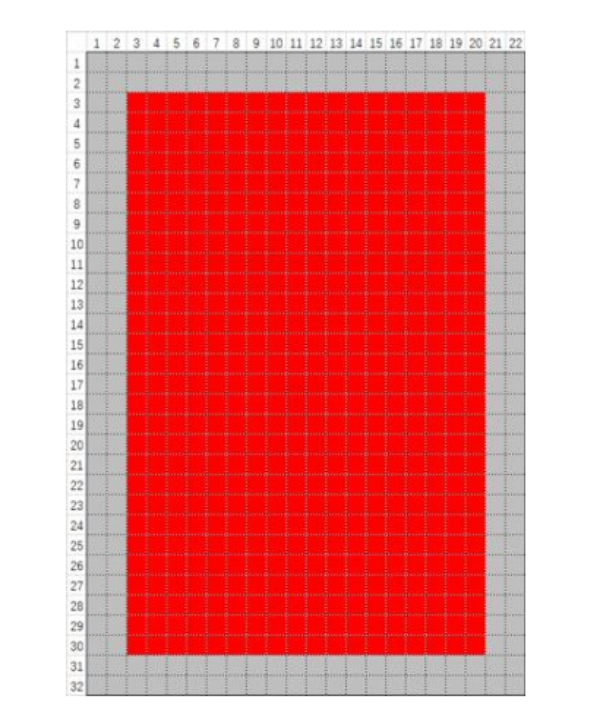

近日,厦门大学与中兴通讯等团队提出了一种基于倒装芯片(FC)的封装结构,将微通道冷却系统集成到大型高功率 CMOS 芯片中,并通过低温铜 - 铜(Cu-Cu)键合工艺实现封装内集成。团队采用创新的低温 Cu-Cu 键合工艺在 8 英寸晶圆上实现 94.48% 高键合率,键合界面热阻低至 1 K・mm²/W(优于台积电 2021 年报道的 1.5 K・mm²/W),同时具备 5.31 MPa 拉伸强度与 10.59 MPa 剪切强度,兼顾散热效率与结构稳定性。采用硅基直槽式微通道(通道宽 300μm、鳍宽 100μm、深 250μm),搭配 20% 丙二醇 + 80% 去离子水冷却液,在 1500 mL/min 流速、940W 芯片总功率下,芯片最高温度仅 81℃(远低于 CMOS 芯片 105℃的允许上限),且 30 分钟测试无液体泄漏,压力稳定在 95kPa。整套工艺基于标准倒装芯片(FC)平台,从 8 英寸晶圆制备、微通道 cooler 制造,到 Cu-Cu 键合、凸点制作、PCB 焊接,均采用工业级设备与流程,尤其 FC 封装环节直接适配现有产线,解决传统微通道技术与 2.5D/3D 集成封装的兼容性难题。研究成果以“Wafer-Level Integration of Liquid Cooling Microchannel on CMOS Chips with Cu-Cu Low Temperature Bonding Process”为题发表在《IEEE》期刊。

03

图文导读

技术细节:从结构到流程的系统化创新

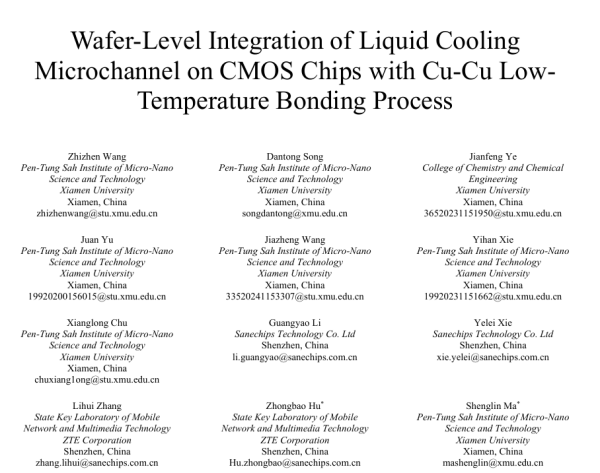

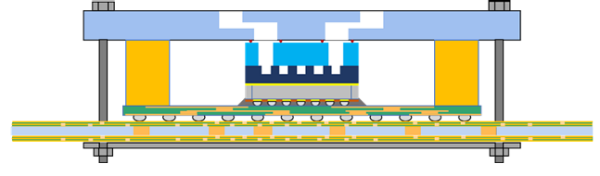

团队设计的 FC 基封装结构,通过 “玻璃盖 - 微通道 - CMOS 芯片” 堆叠架构实现高效散热:玻璃盖采用肖特 BF33 材质,其热膨胀系数与硅匹配,既避免进出口热传导干扰,又通过阳极键合保障高良率;芯片侧采用含 2 金属层 / 3 绝缘层的 TTV(热测试芯片)模拟真实 CMOS 芯片,单个 1.0632mm×1.0632mm 区块内置独立加热器与温度传感器,可精准还原芯片热行为。

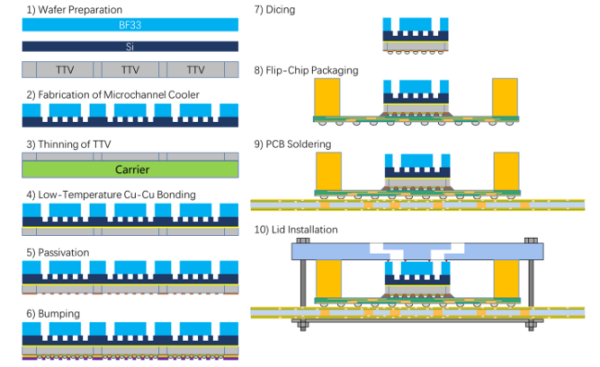

流程上,通过 “分开制造 - 低温键合 - 集成封装” 的思路,先独立制备微通道 cooler 与 TTV 晶圆,再经 250℃、1.5MPa 条件下的 Cu-Cu 键合实现集成,后续通过聚酰亚胺(PI)钝化、Cu/Ni/SnAg 凸点制作(直径 82μm、最小间距 130μm)等步骤,最终完成 65mm×65mm 封装基板的 FC 键合与 PCB 组装,全流程关键节点经扫描声学断层扫描(SAT)验证,无明显缺陷扩展。

应用价值与未来方向

该成果不仅为英伟达 Blackwell GPU 等 1000W 级高功率芯片提供了高效散热方案,更填补了微通道液冷技术从实验室走向工业化的空白。未来团队将进一步优化可制造性设计与仿真方法,同时开发封装级、组装级的可靠性评估体系,推动技术向更高功率密度的 2.5D/3D 集成芯片场景落地。

图 1:基于倒装芯片(FC)的集成微通道封装结构示意图,用于实现大型高功率 CMOS 芯片的高效封装内微通道液冷。

图 2:热测试芯片(TTV)结构示意图。红色区域为有源区,包含 28×18 个区块;每个区块的平面尺寸为 1.0632 mm×1.0632 mm,内部嵌入独立加热器与独立温度传感器。

图 3:微通道冷却器三维示意图。整个冷却器的平面尺寸为 34.0224 mm×23.3904 mm,与 TTV 芯片尺寸完全一致;微通道的通道宽度、鳍片宽度、深度分别为 300 μm、100 μm、250 μm。

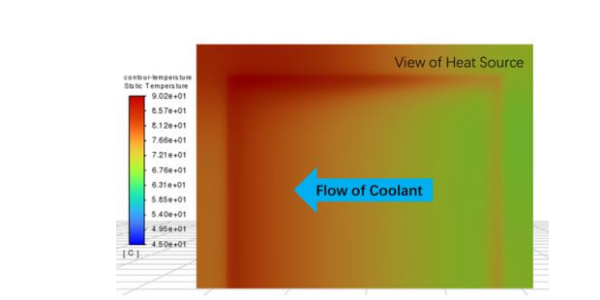

图 4:微通道冷却器半模型仿真结果。冷却液流速设定为 1000 mL/min,流入温度为 45°C;对有源区施加 200 W/cm² 的均匀热流密度时,仿真得到的压力降为 58 kPa,最高温度为 90°C。(图中含 “热源视角”“冷却液流向”标注)

图 5:基于倒装芯片(FC)的集成微通道封装结构制备工艺流程示意图。

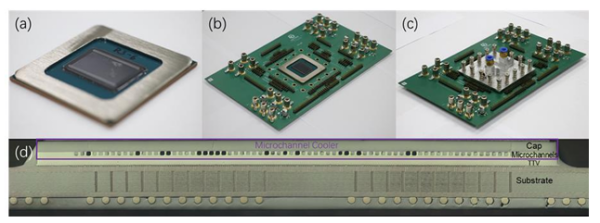

图 6:制备样品实物图:(a)倒装芯片(FC)封装后;(b)PCB 焊接后;(c)盖板安装后的最终样品;(d)倒装芯片(FC)封装后的样品横截面。

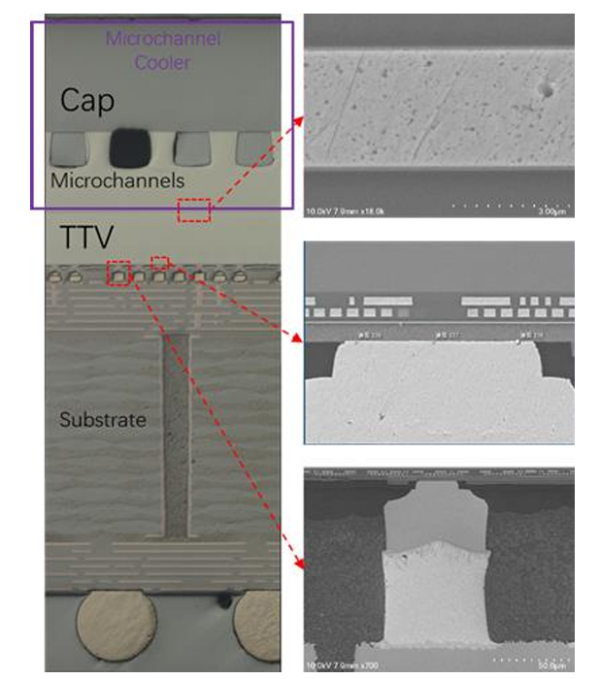

图 7:倒装芯片(FC)封装样品局部区域横截面图:(a)整体视图;(b)低温铜 - 铜(Cu-Cu)键合界面;(c)热测试芯片(TTV)的金属层与钝化层;(d)凸点与封装基板焊盘的键合结构。

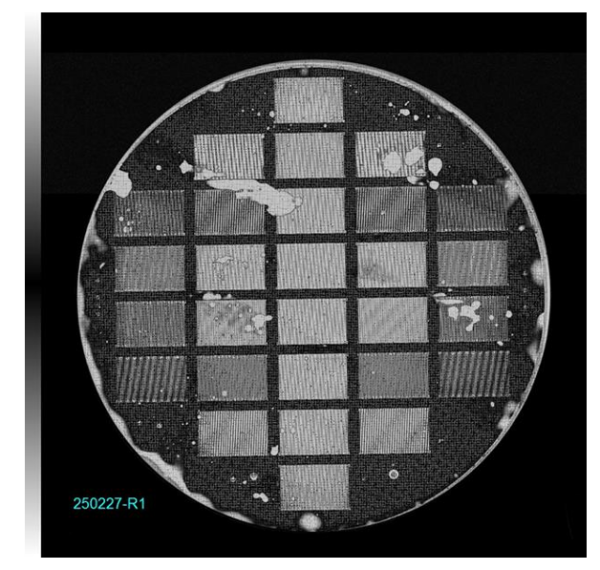

图 8:低温铜 - 铜(Cu-Cu)键合后键合晶圆的扫描声学断层扫描(SAT)图像(标注日期:250227-R1)。

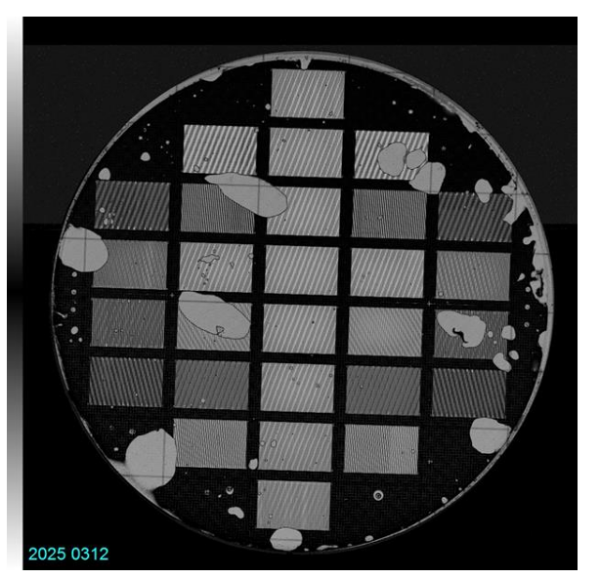

图 9:聚酰亚胺(PI)钝化处理后键合晶圆的扫描声学断层扫描(SAT)图像(标注日期:20250312)。

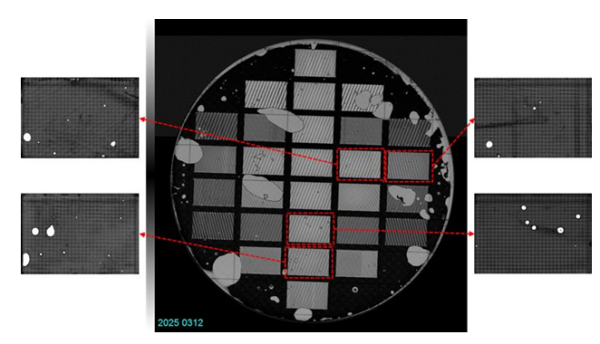

图 10:倒装芯片(FC)键合后堆叠芯片的扫描声学断层扫描(SAT)图像(与图 9 结果对比)。

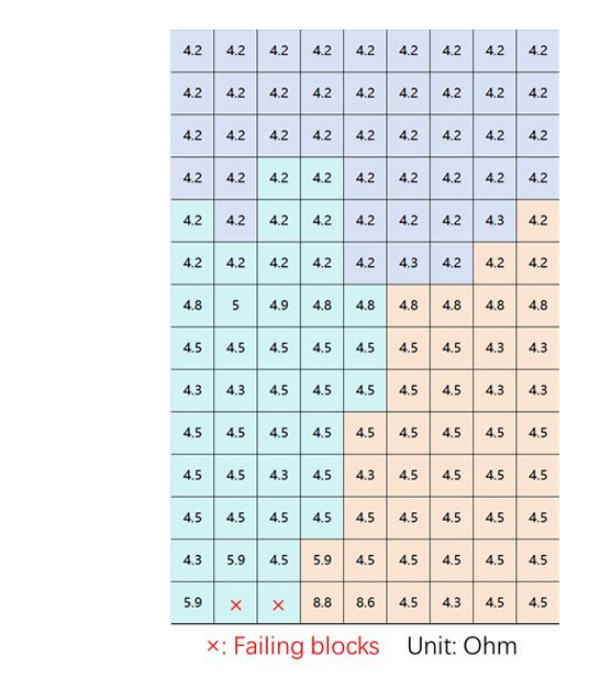

图 11:4 区块组加热器电阻分布图(标注:“x:失效区块”“单位:欧姆”)。

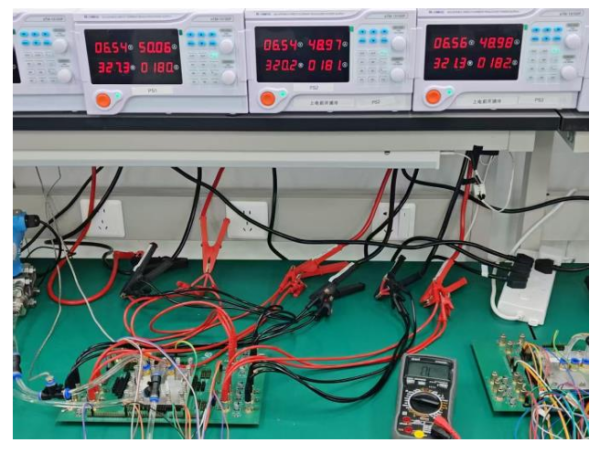

图 12:液冷测试中的组装后样品实物图。