微通道液冷的崛起!下一代芯片冷却技术的突破与路径

来源 | IEEE

链接 | https://doi.org/10.1109/ECTC51529.2024.00072

01

背景介绍

在高性能计算(HPC)领域,芯片性能提升正被一个难题卡住 —— 散热。随着 2.1D、2.3D、2.5D、3D 等先进封装技术普及,芯片集成度更高,但也让系统功率密度飙升,相邻或堆叠芯片间热流密度、热串扰大幅增加,传统风冷完全扛不住了。

风冷受系统设计限制,多数场景散热功率超不过 500W,一旦超标,风扇功率、散热器成本、噪音都会暴涨,根本满足不了 HPC 需求。行业虽尝试过冷板(单相 / 双相)和浸没式冷却,前者靠优化结构提效,后者用低沸点流体被动散热(能处理 0.5-1.0 W/mm² 热流密度),但要么效果有限,要么需重构系统,仍难破解高密散热难题。

正是这样的背景下,硅微通道冷却技术进入视野 —— 它能让冷却液贴近芯片热源,大幅降低热阻。早在 2013 年,美国 DARPA 就启动 ICECool 项目,目标开发 “嵌入式冷却”,实现 kW/cm² 级热流密度散热,还探索将微流控冷却融入衬底、芯片设计初期。而SEMI 发起的 “硅微通道研究”,更是直指核心:找出这项技术迟迟没商业化的原因,推动它从实验室走向量产。毕竟对 HPC 来说,要突破性能天花板,解决散热问题,硅微通道冷却或许是最关键的一步。

02

成果掠影

近日,台积电、Meta、ASE、Google、HP、SEMI、EV Group、Paul Benning等巨头联合发布了关于迈向微通道的芯片热管理文章。在高性能计算(HPC)芯片散热需求激增的背景下,硅微通道直接冷却技术凭借显著优势,成为突破先进封装热瓶颈的关键方向,其核心成果与商业化推进路径已逐渐清晰。

一、技术核心价值:破解先进封装散热困局

先进封装(2.1D/2.3D/2.5D/3D 等)虽提升芯片集成度,却使系统功率密度飙升,热流密度与芯片间热串扰大幅增加,传统风冷(上限<500W)完全无法应对。而硅微通道冷却通过让冷却液贴近芯片热源,能显著降低热阻 —— 相比风冷单芯片 100-130W 的散热能力,嵌入式微通道冷却可实现 1-1.5kW 散热,部分方案甚至能应对 kW/cm² 级热流密度,为高功率 HPC 芯片提供了可行解。

二、关键技术成果:从性能突破到方案落地

1. 散热性能屡创佳绩

·实验室级突破:早在 1981 年,Tuckerman 团队就用硅微通道实现 790W/cm² 散热;1988 年 Phillips 团队用 InP 微通道将这一数据提至 1056W/cm²;近年 Schultz 团队通过嵌入式通道设计,让微处理器核心实现超 350W/cm² 散热,局部热点可扛住 2kW/cm² 热流。

·实用化进展:Hung 团队基于 CoWoS 封装的液态冷却方案,实现 2kW 热设计功率;van Erp 团队用硅衬底做微通道,仅 60mW 泵功就冷却了 GaN-on-Si 芯片 417W/cm² 的器件级热流,兼顾效率与能耗。

2. 技术方案持续优化

·微通道冷板:已用于量产 HPC 封装,热阻从早期 “双热界面材料(TIM1+TIM2)” 结构的 80-100℃・mm²/W,演进到取消 TIM2 的 40-60℃・mm²/W,当前正研发 “冷却液直触硅背面” 方案,热阻可降至 30℃・mm²/W,同时衍生出深反应离子刻蚀(DRIE)高纵横比通道、3D 打印聚合物射流冷板等创新结构。

·器件背面集成:直接在芯片背面刻蚀微通道或集成微针翅热沉,减少热传导路径,如 Sarvey 团队将微针翅热沉集成到倒装键合硅片背面,Bergendahl 团队的五层堆叠硅微冷却器实现 136-182W/cm² 散热。

3. 设计与制造更趋成熟

·架构创新:歧管微通道通过多位置进液缩短流路,降低 29% 压降;自适应水凝胶针翅设计可动态分配流量,针对性解决芯片热点问题。

·制造适配:HP 等企业将激光烧蚀、DRIE 等硅加工技术用于量产,探索晶圆级微通道集成 —— 针对 SoC 与 HBM 不同高度场景,可将微通道刻在独立晶圆上再键合,或在芯片堆叠后整体集成,适配先进封装需求。

三、商业化推进:明确路径与关键动作

1. 核心挑战已清晰

需解决三方面关键问题:一是适配 HPC 封装尺寸升级(如 2.5D 封装中介层将达 100mm×100mm),微通道需同步规模化;二是整合流程,需将微通道集成纳入 SoC 制造、测试及服务器安装环节,平衡良率与成本;三是 coolant 与系统适配,如 PFAS 类冷却液 2025 年将停产,需寻找替代方案,同时提升冷却系统过滤精度以适配<100μm 微通道。

2. 下一步关键动作

·技术验证:SEMI 建议优先通过 CHIPS 计划资助的先进封装试点工厂,测试微通道冷却原型;同时启动 “硅微通道二期” 项目,组建行业团队开发测试载体,验证技术可行性。

·生态协同:需联合数据中心、 coolant 厂商、设备商等,明确 SoC 封装设计规范、冷却液材料兼容性标准,开发专用 EDA 工具解决冷却通道与电路布线的冲突,推动全产业链协同。

硅微通道冷却技术已从实验室走向实用化关键阶段,随着行业协同推进,有望成为下一代 HPC 芯片散热的核心方案,破解性能提升的热瓶颈。研究成果以“Moving Towards Microchannel-based Chip Cooling”为题发表在《IEEE》期刊。

03

图文导读

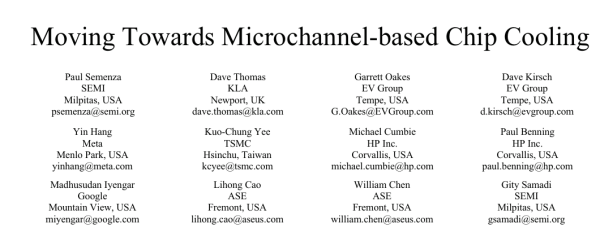

图 1 2.5D 液体冷却趋势(来源:台积电)

左图:传统结构 —— 芯片封装外围设引脚,引脚与芯片间有热界面材料层(TIM1),冷板内置在外壳中,与封装引脚间另设一层热界面材料(TIM2),热阻(TR)为 80~100℃・mm²/W。

中图:集成优化结构 —— 组装时取消 TIM2,封装供应商在封装外围做边缘,系统厂商集成冷板,热阻降至 40~60℃・mm²/W,该结构已投入应用。右图:研发中结构 —— 冷却液直接接触硅片背面,进一步降低热阻至约 30℃・mm²/W;但因无完全封闭的冷板,存在冷却液渗入封装导致短路的风险,需与封装协同设计,通常由晶圆代工厂 / 封测厂(OSAT)完成。

标注说明:图中 “Inlet” 为冷却液入口,“Outlet” 为冷却液出口,展示了不同结构下冷却液的流通路径。

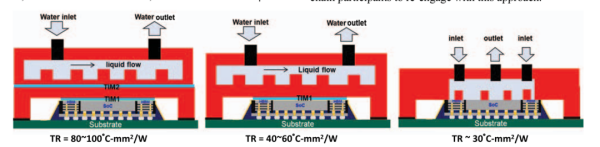

图 2 并行微通道考量(堆叠冷却方式示意图)

展示了芯片堆叠场景下三种微通道冷却方案的位置设计:

·堆叠顶部冷却:最易实现,当前封装顶部可通过传统散热器接触冷却,无需大幅改造现有结构。

·堆叠内部冷却:实用性最强,能将冷却结构嵌入片上系统(SoC)处理器内部 —— 此处为热源核心区域,但集成难度最高,需在主芯片上直接刻蚀微通道。

·堆叠底部冷却:挑战最大,需与输入输出(I/O)接口、供电线路共用空间,存在性能约束权衡;对于 3D 集成电路(3D IC),堆叠中两个芯片间的流体导流属于底部冷却的特殊形式,需改进中介层与键合技术。

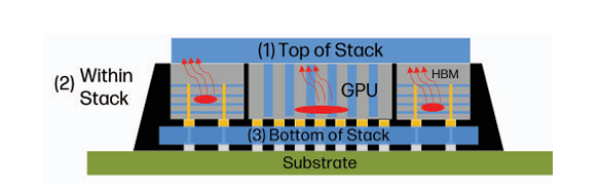

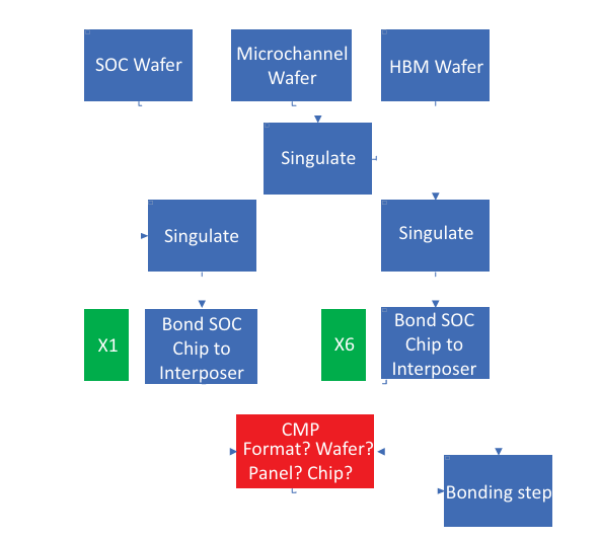

图 3 不同高度的 SoC 与 HBM 堆叠工艺流程

针对系统级芯片(SoC)与高带宽内存(HBM)高度不同的场景,硅微通道制备与集成流程如下:

·分别在独立晶圆上刻蚀硅微通道,得到 “微通道晶圆”;

·将“微通道晶圆”分别与 SoC 晶圆、HBM 晶圆进行键合;

·对键合后的晶圆组合体进行切割(Singulation),使每个 SoC 芯片、HBM 芯片都分别键合有一个微通道芯片;

·最后将带有微通道芯片的 SoC 芯片、HBM 芯片分别键合到中介层(Interposer)上,完成堆叠集成。

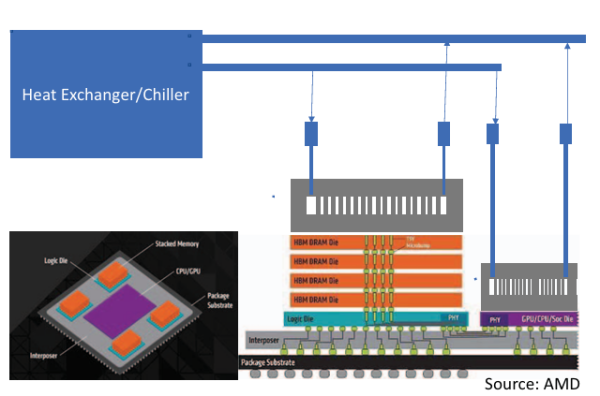

图 4 SoC 与 HBM 堆叠垂直高度简化图(来源:AMD)

直观展示 SoC 芯片与 HBM 芯片在堆叠结构中的垂直空间分布关系,清晰呈现二者高度差异(对应图 3 的应用场景);

标注 “Heat Exchanger/Chiller”(换热器 / 冷却器),提示后续需通过微通道与外部冷却设备衔接,实现热量导出。

图 5 SoC 与 HBM 高度相近时的工艺流程(博世工艺步骤)

针对 SoC 与 HBM 高度相近的场景,流程如下:

·分别对 SoC 晶圆、微通道晶圆、HBM 晶圆进行单独切割(Singulate);

·将切割后的 SoC 芯片通过 X1 键合方式连接到中介层,HBM 芯片通过 X6 键合方式连接到中介层;

·对键合后的结构进行化学机械抛光(CMP)处理,确保表面平整;

·明确需确认集成格式(晶圆级 / 面板级 / 芯片级),最后通过键合步骤将微通道结构与整个芯片封装(含 SoC、HBM、中介层)集成。

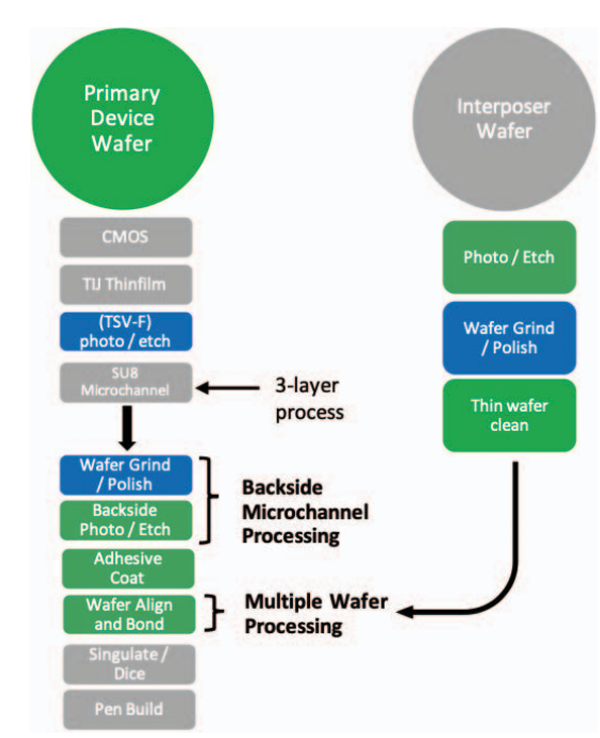

图 6 惠普(HP)用于工业打印头的微通道晶圆工艺流程

展示 HP 将硅微通道集成到 MEMS(微机电系统)器件(工业打印头)的量产流程,对 HPC 领域微通道制造有参考价值:

·主器件晶圆处理:依次进行 CMOS 光刻 / 蚀刻(Photo/Etch)、薄膜(Thinfilm)制备、再次光刻 / 蚀刻,形成基础器件结构;

·中介层晶圆处理:先进行微通道工艺(Microchannel process),再制备 3 层薄膜,随后对晶圆进行研磨 / 抛光(Grind/Polish);

·背面处理:对主器件晶圆背面进行研磨 / 抛光,再通过光刻 / 蚀刻制作背面微通道(Backside Microchannel);

·集成组装:涂覆黏合剂(Adhesive),将主器件晶圆与中介层晶圆对准并键合,进行多晶圆协同处理,最后切割(Singulate/Dice)成单个芯片,完成 “笔形结构”(Pen Build)组装,形成可量产的微通道冷却打印头器件。