西交团队,微通道液冷实现多芯片阵列仅1.5℃温差

来源 | Applied Thermal Engineering

链接 | https://doi.org/10.1016/j.applthermaleng.2025.127803

01

背景介绍

在多芯片阵列电子系统中,大量的热源和发热的复杂性使得热管理结构必须同时解决每个热源的热要求,同时确保所有芯片的温度均匀性和足够的散热性能。这些要求对冷却结构的设计提出了重大挑战。尽管歧管冷却剂分布结构显著提高了温度均匀性,冷板冷却仍然面临性能限制,在芯片和冷板之间存在额外的热扩散阻力导致传热效率的显著降低,使得这种方法不适合于多个高功率芯片的热管理。为了克服冷板冷却的局限性,嵌入式冷却结构需要解决多芯片阵列电子系统中的热管理挑战。

02

成果掠影

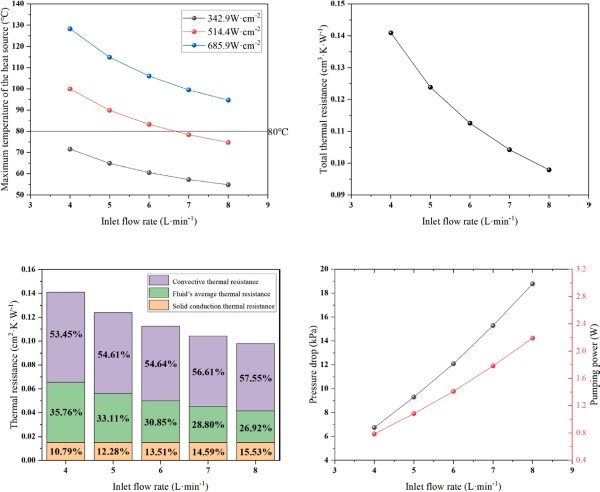

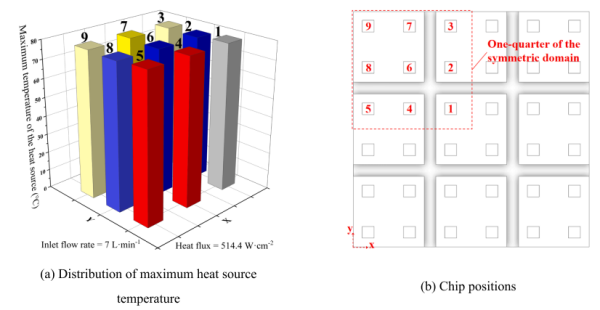

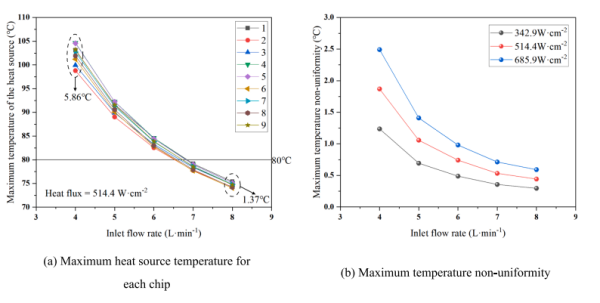

近日,西安交通大学屈治国团队提出了一种多级冷却结构设计方法。该方法以四芯片阵列为基础单元,将大规模多芯片阵列电子系统的冷却结构划分为多个四芯片阵列单元冷却结构,以及用于单元冷却结构间冷却液分配与汇集的歧管结构,从而实现大规模多芯片阵列电子系统嵌入式冷却结构的模块化组装。基于此多级冷却结构设计方法,研制了由四芯片阵列单元冷却结构样件和歧管结构组成的测试装置,并对四芯片阵列进行了实验测试。实验结果表明:在热通量为160.5 W/cm²、冷却液流量为600 ml/min工况下,测试装置的平均热阻为0.037 cm²·K/W;在400 ml/min流量下,平均温度不均匀度仅为1.62℃,展现出良好的散热性能与温度均匀性。基于实验装置的冷却结构设计,进一步开发了36芯片阵列电子系统的嵌入式冷却结构。通过流阻分析和模型简化的仿真手段对冷却结构进行优化,仿真结果表明:优化后的36芯片阵列电子系统嵌入式冷却结构具有优异的热性能、流动性能与温度均匀性。在入口流量7 L/min、总热功率15 kW工况下,各芯片热源最高温度均低于80℃,最大温差仅1.51℃,最高温度不均匀度为0.53℃,压降仅为15.28 kPa。本研究为大规模多芯片阵列电子系统嵌入式冷却结构设计提供了有效方法。研究成果以“Design and thermofluidic performance of multi-level embedded cooling structures for multi-chip array electronic systems”为题发表在《Applied Thermal Engineering》期刊。

03

图文导读

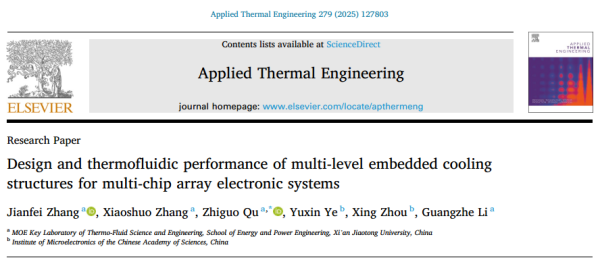

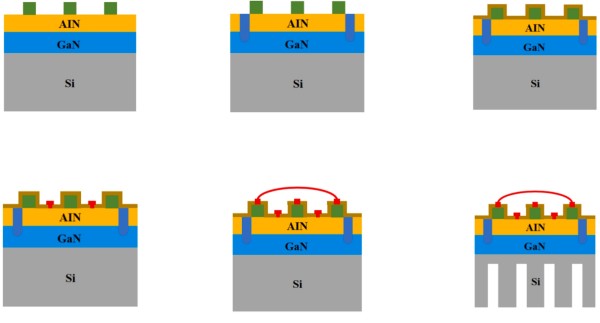

图1.多芯片阵列嵌入式散热结构示意图。

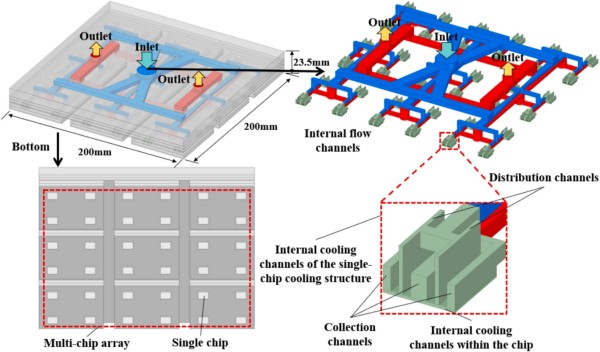

图2.多级设计方法的体系结构。

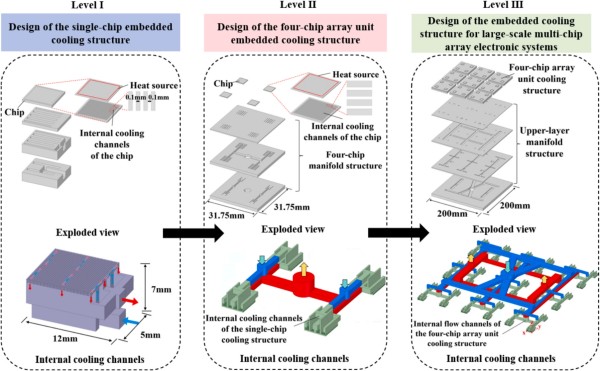

图3.单片嵌入式散热结构示意图。

图4.具有内部冷却通道的测试芯片的制造过程。

图5.用于36芯片阵列电子系统的嵌入式冷却结构的热耗散和流动性能。

图6.最高热源温度分布及对应的芯片位置。

图7.最高热源温度变化与最高温度不均匀性。