郝跃院士团队 | 从金刚石到微通道,电子器件热管理综述

来源 | IEEE TRANSACTIONS ON ELECTRON DEVICES

链接 | https://doi.org/10.1109/TED.2025.3562506

01

背景

近年来,宽禁带(WBG)及超宽禁带(UWBG)半导体器件在电力电子和射频(RF)领域的应用持续扩张,凭借更高的临界电场、更高的载流子迁移率、更低的导通电阻和开关损耗,这类器件在能源转换与通信领域展现出显著优势。其中,GaN 器件已从实验室走向产业化,全球 GaN 功率器件市场在 2023 年达到 175 亿美元,预计未来几年将保持 20%以上的年均增长。与此同时,Ga₂O₃ 等 UWBG 材料在过去十年成为高功率电子的研究热点,被视为下一代电力电子的重要突破口。

随着 5G 通信、新能源汽车、高速铁路、数据中心等行业的迅速发展,WBG 与 UWBG 器件的高频、高功率密度特性被不断推向极限。然而,热管理问题已成为制约其性能释放和长期可靠性的核心瓶颈——在高功率工作条件下,自热效应会显著升高结温,导致器件电性能衰退、甚至失效。例如,Ga₂O₃ 由于本征热导率低,仅为 GaN 的十分之一左右,散热困难更为突出;GaN HEMT 在栅极附近的高热流密度甚至可达到数十kW/cm²,局部热点分布极不均匀,容易引发栅极烧毁。

在当前产业趋势下,WBG/UWBG 器件正朝着更小芯片尺寸、更高开关频率、更紧凑封装方向演进,这虽带来更高的功率密度与能效,却也加剧了散热难度。如何在有限空间内高效导热、快速降温,直接决定了器件能否稳定工作及其市场化进程。因此,从芯片内部结构优化到外部封装与冷却策略,全方位的器件级热管理技术,正成为推动 WBG/UWBG 半导体产业化的关键突破口。

02

成果速览

近日,西安电子科技大学郝跃院士、冯欣副教授,周弘教授、张进成教授团队系统综述宽禁带与超宽禁带半导体器件热管理技术的最新进展。该综述涵盖从器件内部结构优化(包括版图优化、衬底减薄、高热导率衬底键合与覆层)至外部热增强策略(如倒装芯片封装、微通道主动冷却及瞬态热管理技术)的全链条技术体系。深入探讨了当前技术瓶颈、潜在解决方案及未来发展机遇,旨在突破关键散热技术壁垒,推动宽禁带与超宽禁带半导体的深度产业化进程。文章总结的主要技术路径包括:

内部热扩散增强:通过器件架构优化、衬底减薄、高导热衬底(SiC、金刚石等)替换与覆盖,降低热阻、缩短传热路径。

先进封装策略:利用倒装芯片封装(flip-chip)、双面散热等方式高效导热。

主动冷却手段:引入微通道冷却、流体热管理等主动方式显著提升散热效率。

瞬态热管理技术:针对脉冲高功率或浪涌条件下的快速热积累,提出了多种瞬态抑热方案。

综述中不仅对这些技术的原理、性能提升幅度、适用场景进行了对比分析,还深入讨论了当前存在的关键技术挑战及潜在解决方向,例如降低界面热阻(TBR)、兼顾散热性能与工艺可行性、平衡性能与成本等。该文为 WBG/UWBG 器件的产品级设计提供了系统化的热管理思路和技术储备,有助于加速功率器件在 5G 通信、电动交通、工业电子等高功率密度领域的可靠应用与产业化进程。研究成果以“Recent Advances in Device-Level Thermal Management Technologies for Wide Bandgap Semiconductor: A Review”为题发表在《IEEE TRANSACTIONS ON ELECTRON DEVICES》期刊。

03

图文导读

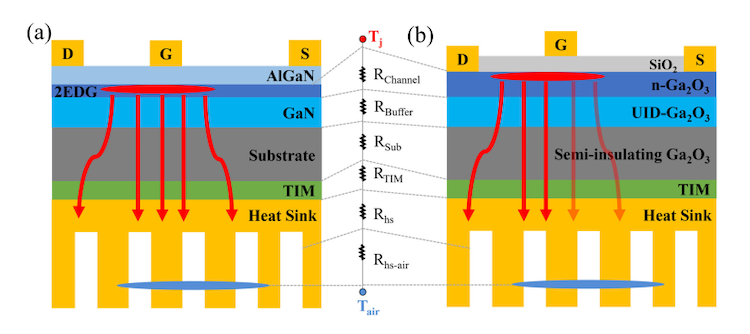

图1. Thermal dissipation pathway and equivalent thermal resistance

model for (a) GaN HEMT and (b) Ga2O3 MOSFET.。

图1展示了GaN HEMT与Ga₂O₃ MOSFET在工作时的热点分布、散热路径及等效热阻模型,其中GaN HEMT的热量主要集中在靠近漏极的栅极下方,受电场聚集影响明显,其散热瓶颈主要来自GaN与外延衬底间较大的热边界电阻(TBR);而Ga₂O₃ MOSFET虽然TBR较小,但由于材料本征热导率极低(0.11–0.27 W/cm·K),整体散热困难,热阻主要来自材料本身。两类器件的热阻均由沟道与缓冲层、衬底、热界面材料(TIM)、散热器以及散热器与空气的对流换热构成,高功率工作下热点温升会导致导通电阻上升、输出电流下降等性能衰退,因此热管理策略需因材施策——GaN器件应重点降低TBR以提高热扩散效率,而Ga₂O₃器件则需从提升材料本征导热能力或缩短传热路径入手。

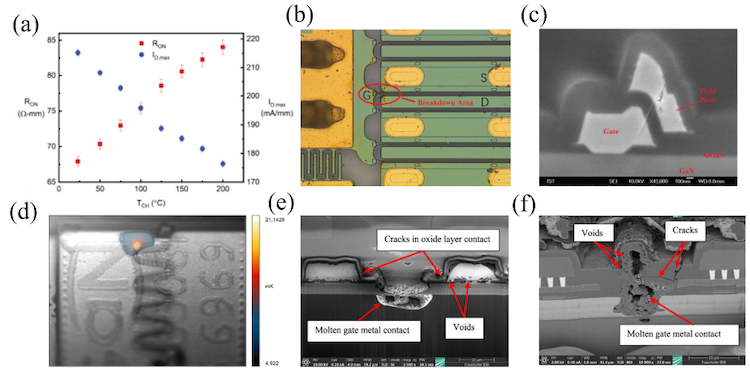

图2. (a) Variation of ID,max and RON of β-Ga2O3 thin-channelMOSFET with channel temperature. Reproduced with permission [17].Copyright 2020, IEEE. (b) Breakdown area of GaN HEMT (CGH-27015).(c) Crack located on the field plate under thermal aggregation. Reproduced with permission [22]. Copyright 2016, IEEE. (d) Hot spoton GaN MISHEMT. Damaged regions on (e) p-GaN HEMT and(f) GaN MIS-HEMT after the unclamped inductive switching (UIS) test.Reproduced with permission [23].

图2展示了Ga₂O₃ MOSFET与GaN HEMT在高温和高功率密度工作条件下的性能衰退与失效形貌,其中(a)表明当Ga₂O₃ MOSFET的沟道温度升高至200 °C时,其最大输出电流ID显著下降约40 mA/mm,同时导通电阻上升;(b)和(c)显示GaN HEMT在高功率脉冲下因局部热点聚集发生击穿及栅极下方裂纹;(d)为GaN MIS-HEMT的热点热成像,温升可达211 °C;(e)和(f)揭示在栅极局部焦耳热超过金属熔点时,p-GaN HEMT与GaN MIS-HEMT均出现金属层熔化和损伤。整体来看,无论是低热导率的Ga₂O₃器件还是2DEG沟道极薄的GaN器件,高热流密度与不均匀的热分布都会导致性能快速衰退甚至失效,突显了在高功率密度器件中实施高效散热与热点控制的重要性。

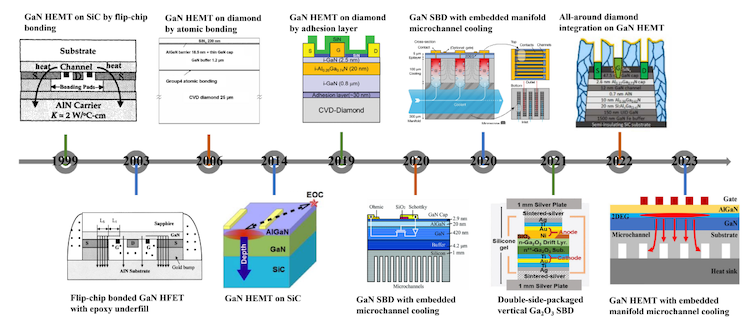

图3. Brief timeline of the development of advanced heat-management technologies for WBG/UWBG. Inset images: “GaN HEMT on SiC by flip-chip bonding” reproduced with permission [32]. Copyright 1999, IEEE. “Flip-chip bonded GaN HFET with epoxy underfill” reproduced with permission [33]. Copyright 2003, IEEE. “GaN HEMT on diamond by atomic bonding” reproduced with permission [34]. Copyright 2006, IEEE.“GaN HEMT on SiC” reproduced with permission [35]. Copyright 2014, Wiley-VCH. “GaN HEMT on diamond by adhesion layer” reproducedwith permission [36]. Copyright 2019, IEEE. “GaN SBD with embedded microchannel cooling” reproduced with permission [37]. Copyright 2020,IEEE. “GaN SBD with embedded manifold microchannel cooling” reproduced with permission [38]. Copyright 2020, Nature Publishing Group.“Double-side-packaged vertical Ga2O3 SBD” reproduced with permission [39]. Copyright 2021, IEEE. “All-around diamond integration on GaN HEMT” reproduced with permission [40]. Copyright 2022, IEEE. “GaN HEMT with embedded manifold microchannel cooling” reproduced with permission [41].

图3以时间轴的形式梳理了WBG/UWBG器件先进热管理技术的发展历程,涵盖了从1999年至2023年间具有代表性的关键成果:早期的技术如1999年的“SiC衬底倒装键合GaN HEMT”与2003年的“环氧填充倒装GaN HFET”主要集中在通过封装方式改善散热;2006年出现了“原子键合金刚石衬底GaN HEMT”,标志着高导热材料引入器件底部的尝试;2014年的“GaN-on-SiC”成为产业主流方案之一;2019年进一步发展到“金刚石衬底粘结层GaN HEMT”,降低了界面热阻;2020年首次出现了嵌入式微通道冷却的GaN SBD与流道分配式微通道冷却技术,大幅提升主动冷却效率;2021年推出了双面封装的垂直Ga₂O₃ SBD;2022年实现了器件全包覆金刚石散热;2023年则将流道分配式微通道冷却与GaN HEMT集成。该图直观呈现了器件热管理技术从被动导热到主动冷却、从单一结构优化到多技术融合的演进趋势,为后续散热方案的选择与研发提供了历史脉络和参考方向。

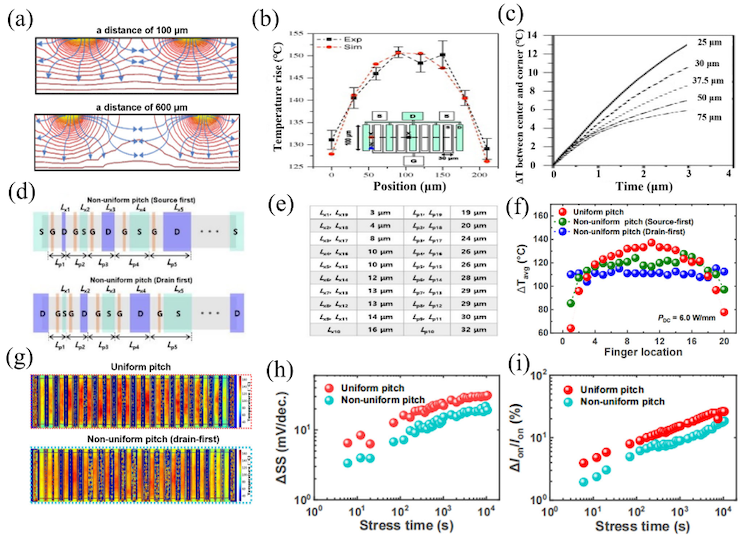

图4. (a) Simulated isothermal and heat flux streamlines of GaN HEMT by increasing gate distance. Reproduced with permission [41]. Copyright 2023, IEEE. (b) Temperature distribution on multifinger GaN HEMT under 10 W/mm. (c) Relationship of temperature difference with the increasing distance from center to corner on multifinger GaN HEMT under 10 W/mm. Reproduced with permission [44]. Copyright 2011,Elsevier. (d) Two kind layouts on multifinger GaN HEMT and the relateddistance parameters in (e). (f) Simulated temperature difference with different layouts and the corresponding temperature distribution under 6.0 W/mm in (g). Degradation of (h) SS and (i) ion with different layout under applied stress. Reproduced with permission [45].

图4展示了通过平面结构优化改善多指GaN HEMT器件散热性能的研究结果,模拟与实测均表明,多指结构中中央指的温度明显高于边缘指,典型温差可达约20 °C,这是由于相邻指间热耦合导致的热点聚集。为缓解这一问题,一种常见方法是增大相邻指间距,例如将漏源间距从30 µm增加至75 µm,可使中央指温度下降约7 °C;另一种方法是采用非均匀指距布局,使热分布更均匀,平均表面温度可降低约20 °C,并显著减轻阈值摆幅(SS)与开启电流(ION)的退化。此外,还有研究通过微型器件阵列优化功率放大器布局,有效降低峰值结温并保持较高的有效功率密度。总体来看,平面结构优化可降低热点温度、提升器件可靠性和功率密度,但其对平均温度的改善有限,且主要适用于多指射频器件,应用范围相对受限。

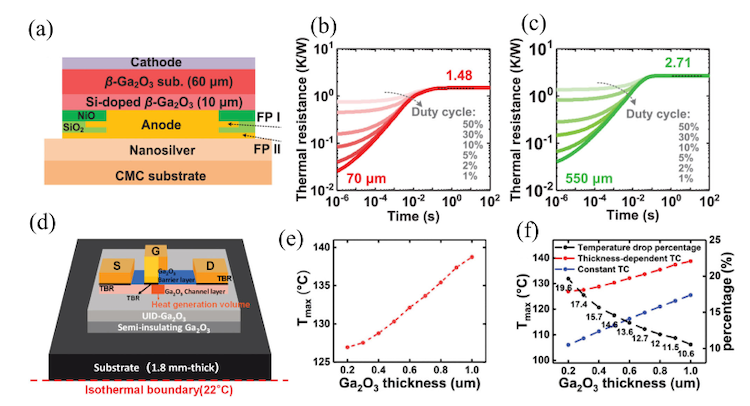

图5. (a) Schematic representation of flip-chip Ga2O3 SBD. Timedependent thermal resistance curves under varying duty cycles for Ga2O3 SBDs with substrate thickness of (b) 70 µm and (c) 550 µm. Reproduced with permission [49]. Copyright 2022, IEEE. (d) Schematic representation of a β-Ga2O3 FET. (e) Tmax versus β-Ga2O3 thickness (tG) (ranging from 0.2 to 1 µm). (f) Tmax versus tG under the varying or constant thermal conductivities. Reproduced with permission [50].

图5展示了通过衬底减薄降低热传导路径、提升Ga₂O₃器件散热性能的效果以及厚度变化对器件温升的影响。研究表明,当Ga₂O₃ SBD的衬底厚度由550 µm减薄至70 µm时,器件热阻由2.71 K/W降至1.48 K/W,降低约45%;模拟结果进一步说明,在相同功率密度(1.8 W/mm)下,Ga₂O₃厚度从0.2 µm增加至1 µm会导致器件最高温度上升约12 °C,这是由于Ga₂O₃厚度增加会降低其有效热导率。衬底减薄能有效缩短热传导距离、增加热流密度,从而加快散热速度,但过度减薄会削弱半导体芯片的机械强度,使晶圆易碎,并对后续器件加工带来挑战,因此在实际应用中需要在热性能提升与机械可靠性之间取得平衡。

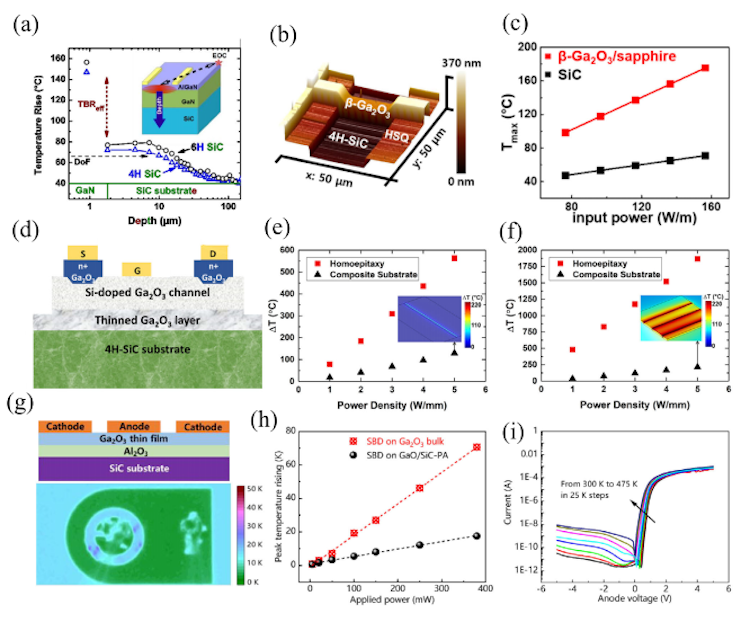

图6. (a) Temperature rises versus depth on GaN HEMT on SiC substrate under power density of 30 W/mm. Reproduced with permission [35]. Copyright 2014, Wiley-VCH. (b) AFM image of β-Ga2O3 FET on 4H-SiC substrate. (c) Tmax versus input power with different substrates. Reproduced with permission [55]. Copyright 2020, Electrochemical Society. (d) Schematic of Ga2O3 MESFET. Tmax versus power density on (e) single-finger (f) six-finger and Ga2O3 MESFET with different substrates under 5 W/mm. Reproduced with permission [56]. Copyright 2021, American Chemical Society. (g) Surface temperature image under an input power of 380 mW for Ga2O3 SBD on SiC by ion-cutting technique. (h) Peak temperature rising versus applied power with different substrates. (i) Temperature-dependent I–V characteristics.Reproduced with permission [57].

图6比较了不同高导热衬底(尤其是SiC)对GaN和Ga₂O₃器件散热性能的改善效果。对于GaN-on-SiC HEMT,在30 W/mm功率密度下,其GaN与SiC界面温差可达80 °C,显示SiC良好的导热优势;对于Ga₂O₃器件,模拟结果表明,在相同输入功率下,SiC衬底可使Ga₂O₃ FET峰值温度比蓝宝石衬底低约100 °C,且Ga₂O₃ MESFET在SiC衬底上的表面温度仅150 °C,而同条件下同质外延Ga₂O₃衬底的温度可高达600 °C,热阻仅为其约11%。此外,通过离子切割将高质量Ga₂O₃转移到SiC衬底的SBD,热阻降至43.55 K/W,在380 mW功率下温差仅17.46 °C,并显著降低漏电流。整体来看,SiC作为高导热衬底不仅能显著降低器件结温,还能提升功率密度与可靠性,是目前UWBG器件(特别是Ga₂O₃)最具产业化可行性的散热衬底方案之一。

图7. (a) Schematic representation of β-Ga2O3 RF power FET on SiC substrate. (b) Small-signal RF characteristics. (c) Large-signal class-AB performance. Reproduced with permission [58]. Copyright 2023, IEEE. (d) Schematic of β-Ga2O3 RF MOSFET on SiC. (e) Small-signal RF characteristics. (f) Large-signal performance with a LG of 0.1 in 2-GHz CW mode. Reproduced with permission.

图7展示了基于SiC衬底的β-Ga₂O₃射频功率器件的性能表现及其在高功率微波应用中的潜力。利用离子切割与剥离工艺制备的β-Ga₂O₃-on-SiC MOSFET,在2 GHz连续波条件下实现了27.6 GHz的fT、57 GHz的fmax,输出功率密度达到2.3 W/mm、功率附加效率(PAE)为30%;通过沟道掺杂优化的β-Ga₂O₃ RF MOSFET更是将fT提升至47 GHz,展示出优异的高频性能。这些结果表明,SiC不仅为Ga₂O₃器件提供了显著的热扩散能力,也支持其在高频高功率场景下实现更高增益与效率,为UWBG器件进军高功率微波与射频领域奠定了技术基础。

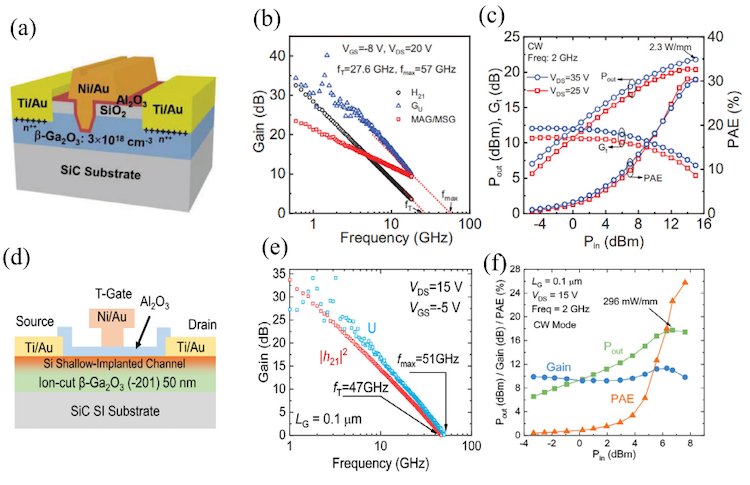

图8. (a) Output characteristics of GaN HEMT after substrate transfer. (b) Temperature rise in each layer of GaN HEMTs based on different TBR and substrate under 10 W/mm. Reproduced with permission [62]. Copyright 2017, IEEE. (c) Schematic cross section of the n-polar GaN HEMT with the top integrated diamond. (d) STEM of the sample showing a 30-nm nucleation layer and <1 nm Si3N4. Reproduced with permission [64]. Copyright 2021, American Chemical Society. (e) Schematic of GaN HEMT on diamond substrate by CVD method. (f) ID reduction and (g) temperature rise versus power density using diamond substrate. Reproduced with permission [36]. Copyright 2019, IEEE. (h) Steady-state thermal reflection images of GaN HEMT on Si substrate at 17.1 W/mm (left), and GaN HEMT on diamond substrate at 24.2-W/mm dc output power (right). (i) Average temperature variation in the gate–drain access region versus dc power. Reproduced with permission [65].

图8展示了利用高导热金刚石衬底提升GaN HEMT散热性能的研究成果。实验结果表明,将GaN外延结构转移到多晶金刚石衬底后,在功率密度为12 W/mm时,器件峰值温度相比原有SiC衬底降低了约40 °C;在更高功率密度(20 W/mm)下,金刚石衬底器件的峰值温度依然显著低于SiC衬底器件。模拟分析进一步揭示,金刚石衬底的高热导率(可达2000 W/m·K)能够显著降低热点温度,并均匀化热分布,从而改善器件在大功率密度下的稳定性和可靠性。总体来看,高导热衬底,尤其是金刚石,正成为突破WBG器件散热瓶颈的关键材料之一,但其高成本和加工难度仍是制约大规模应用的主要挑战。

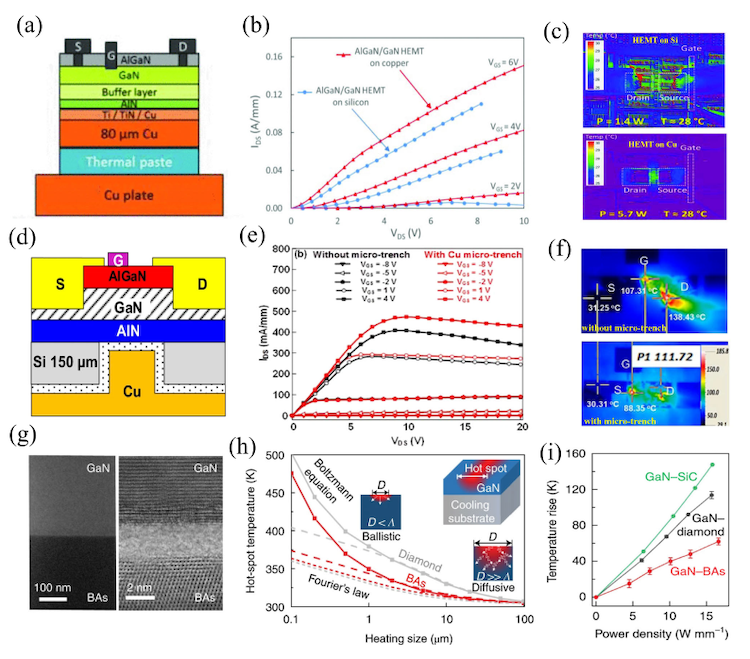

图9. (a) Schematic of GaN HEMT on copper substrate. (b) I–V characteristics. (c) IR thermography images for comparison. Reproduced with permission [72]. Copyright 2019, IEEE. (d) Schematic of GaN HEMT with embedded copper and corresponding I–V characteristics in (e). (f) Thermography images at a power density of 12 W/mm. Reproduced with permission [73]. Copyright 2019, Nature Publishing Group. (g) Cross-sectional SEM (left) and TEM (right) images of GaN HEMT on BAs. (h) Hot spot temperatures versus heating size for two optimal thermal conductors (BAs and diamond). (i) Temperature rise with applied power density. Reproduced with permission [74].

图9展示了通过在GaN HEMT底部外延层与金刚石衬底之间引入不同类型粘结层(BL)来降低热边界热阻(TBR)并提升散热性能的研究结果。测试发现,直接键合的GaN-on-diamond结构虽然具备极高的热导潜力,但由于界面缺陷和声子失配,TBR偏高;引入如AlN、SiN等中间粘结层后,可有效改善界面声子匹配,TBR显著降低,其中AlN BL的效果最佳,使界面热阻降至约10 m²K/GW,相比无BL结构降低近50%,并在高功率密度(20 W/mm)下将峰值温度下降幅度提升至约30 °C。模拟结果进一步验证了BL在高功率条件下的降温作用,表明优化界面层不仅能充分发挥金刚石衬底的高热导率优势,还能提升器件在极端工作环境下的稳定性与寿命。

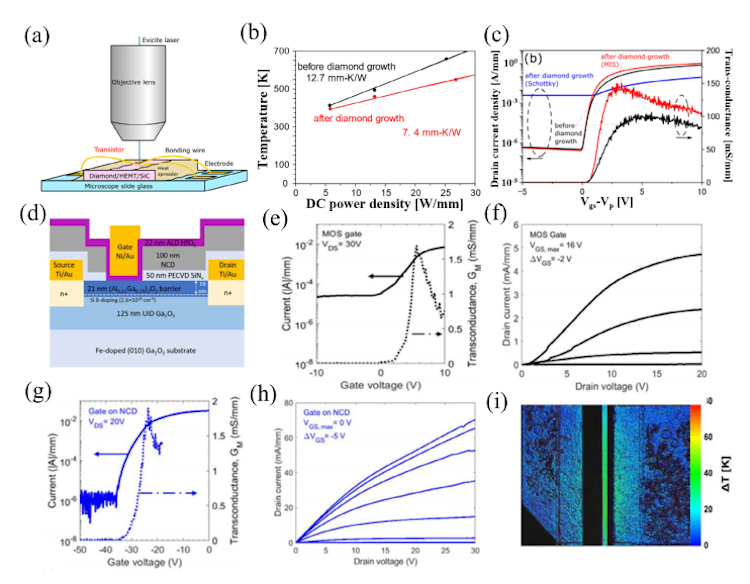

图10. (a) Diagram illustrating the process of temperature measurement of GaN HEMT with diamond on surface using Ramanspectroscopy system. (b) Maximum temperature versus dc power density. (c) Transfer characteristic comparison. Reproduced with permission [75]. Copyright 2021, IOP Publishing. (d) Cross-sectional illustration of β-Ga2O3 HFET featuring a heat-spreading layer of NCD. (e) and (f) DC transfer characteristics and (g) and (h) output characteristics of β-Ga2O3 with MOS or NCD gate, respectively. (i) Thermoreflectance images of β-Ga2O3 HFET with NCD layer at a power density of 1.5 W/mm. Reproduced with permission [76].

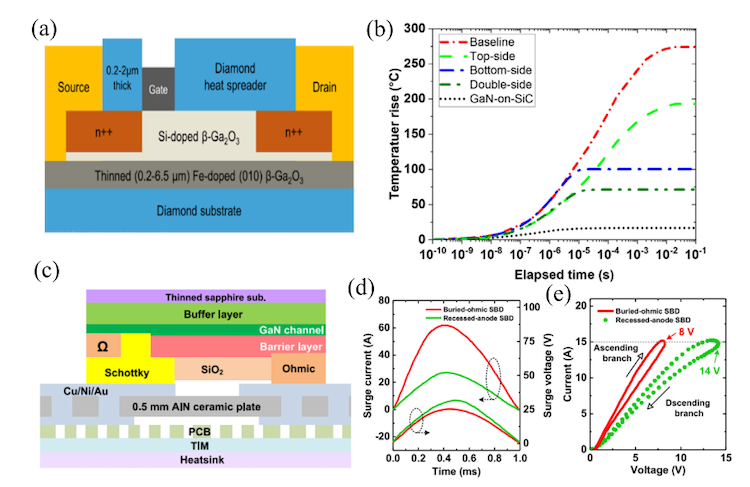

图10展示了不同键合方法对GaN与金刚石衬底界面热阻(TBR)及器件散热性能的影响。研究对比了金属热压键合(AuSn、AuIn)、表面活化直接键合(SAB)、以及化学气相沉积(CVD)直接外延等多种方式,结果表明:金属热压键合工艺可在较低温度下实现稳固结合,但金属层本身热导率有限,TBR依然较高;SAB方法能够在室温下获得较低TBR,且无需中间层,但界面清洁度与原子平整度要求极高;CVD直接在金刚石上外延GaN则可实现最优的界面热传导性能,TBR降至约10 m²K/GW,并在20 W/mm功率密度下将器件结温降低超过40 °C。整体来看,选择合适的键合方式需在热性能、工艺复杂度、成本及器件可靠性之间权衡,其中CVD直接外延虽性能最佳,但目前受限于设备与材料质量控制,尚难大规模产业化。

图11. (a) Thermal reflectance images of GaN HEMTs without/with encapsulated diamond. (b) and (c) I–V characteristics without/with encapsulated diamond, respectively. (d) Temperature versus dc power density. Reproduced with permission [40].

图11展示了在GaN HEMT结构中引入高导热盖层(cap layer)以改善器件表面热扩散的效果。研究采用不同材料(如金刚石、AlN)作为盖层沉积在栅极区域上方,通过有限元模拟与热成像实验发现,高导热盖层能够在热点区域形成横向热扩散通道,将局部高热流密度更均匀地分散到周围区域,从而降低峰值温度;其中金刚石盖层的效果最显著,可在20 W/mm功率密度下使结温下降超过20 °C。进一步分析表明,盖层厚度与热导率的匹配至关重要,过厚会影响器件高频性能,过薄则难以形成有效的热扩散路径。该方法无需改变器件底部封装结构,适合与其他散热策略(如高导热衬底、界面优化)协同应用,以提升高功率密度GaN器件的热管理水平。

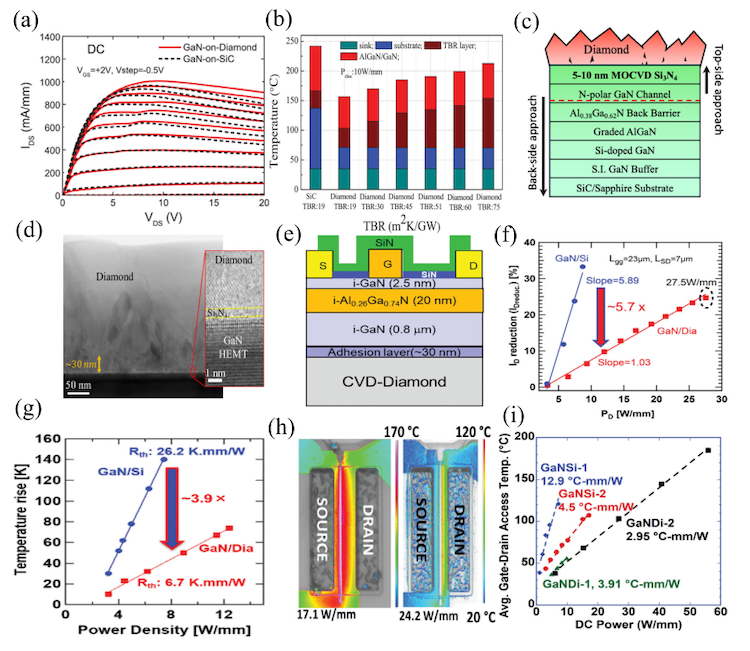

图12. (a) Schematic representation of flip-chip Ga2O3 MOSFET using NCD passivation. (b) Comparison of junction-to-package thermal resistance. (c) Temperature difference versus time with different device structure. Reproduced with permission [82]. Copyright 2019, IEEE. (d) Structure diagram of CAVET device. Model simulation results of CAVET device with (e) bottom-side cooling and (f) double-side cooling. (g) Maximum temperature versus dc power density. Reproduced with permission [87]. Copyright 2021, IEEE. (h) Maximum temperature versus dissipated power density under different cooling schemes. (i) Structure of this double-side cooling Ga2O3 MOSFET. Reproduced with permission [88].

图12展示了两类器件级散热方案的对比与仿真:一是倒装(flip-chip)Ga₂O₃ MOSFET 配合顶层纳米晶金刚石(NCD)封装,示意图、结到封装热阻与瞬态温升曲线表明,通过将器件倒装到金刚石载体并配合热通孔,结-封装热阻可降至约 7 mm·K/W,器件表面温度在测试条件下仅升至约 60°C,显著优于传统结构;二是针对垂直 CAVET/Ga₂O₃ 器件的双面散热(double-side cooling)仿真与比较,结果显示相较于仅底部散热,双面散热可将最大通道温度降低一半以上,并使在相同结温限制下的可用功率密度提高约 5 倍。进一步的界面与封装参数优化(如薄 Ga₂O₃ 层、金刚石衬底、烧结 Ag 与高性能 underfill)在仿真中也将器件热阻降至 ~11 mm·K/W 并实现在结温 200°C 限制下高达 ~16 W/mm 的峰值功率密度,说明倒装+顶层高导热材料与双面散热的组合在提升 Ga₂O₃ 器件热管理能力上具有很强的工程可行性与潜力。

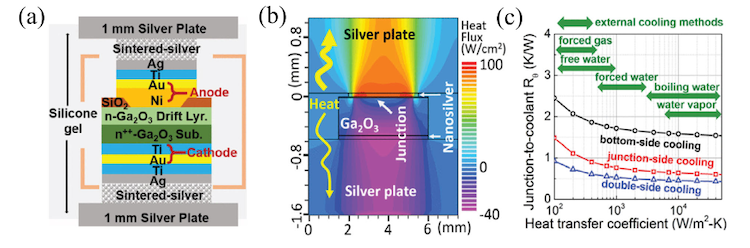

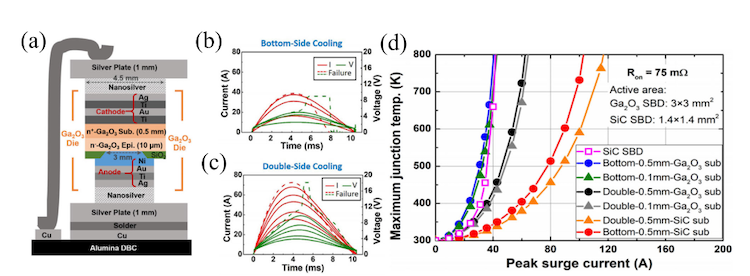

图13. (a) Double-side cooled Ga2O3 SBD structure. (b) Simulated heat flux distribution. (c) Simulated thermal resistance Rθ of Ga2O3 SBD under bottom cooling, junction cooling, and double-side cooling. Reproduced with permission [39].

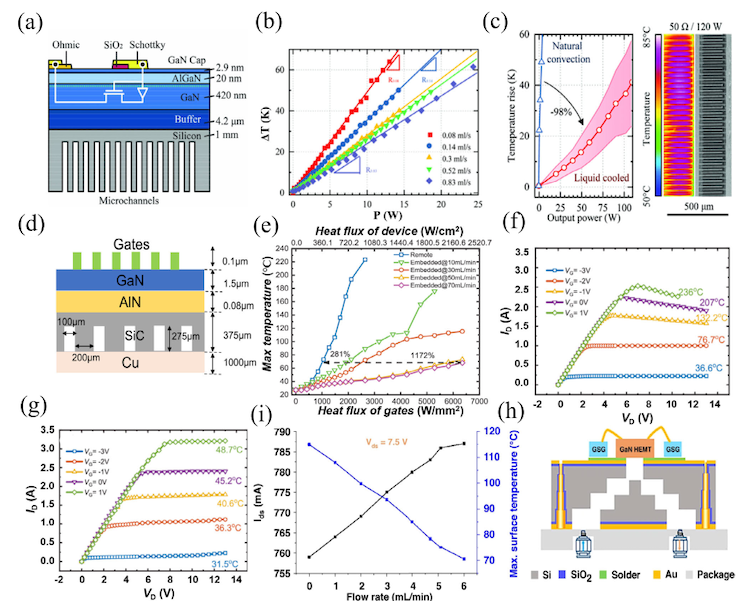

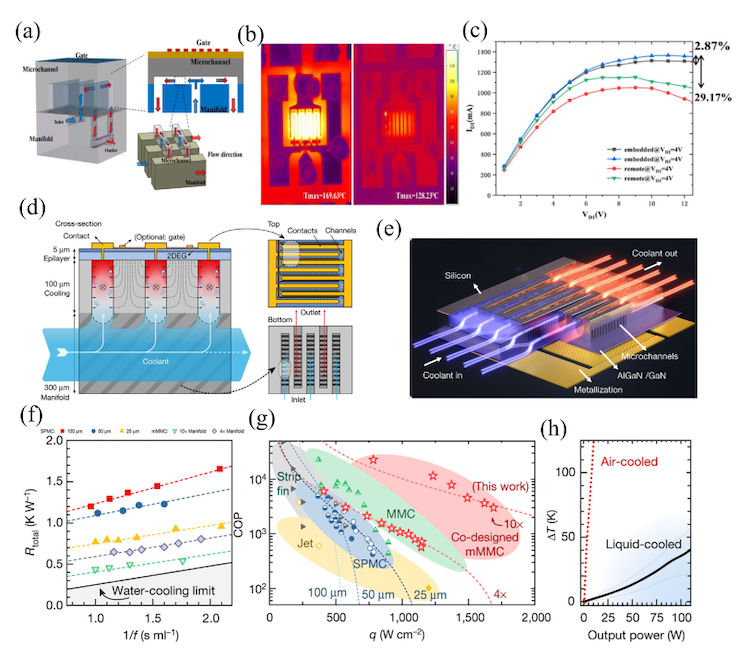

图14. (a) Diagrammatic representation of liquid-cooled GaN SBD. (b) Temperature difference versus dc power density across flow rate sranging from 0.08 to 0.83 mL/s. (c) Performance comparison under different output power and the surface temperature distribution. Reproduced with permission [37]. Copyright 2020, IEEE. (d) Schematic of GaN HEMT structure with an embedded cooling technique. (e) Correlation between temperature and heat flux in both remote and embedded cooling scenarios. I–V characteristics of (f) remote cooling and (g) embedded cooling at a flow rate of 50 mL/min. Reproduced with permission [92]. Copyright 2022, IEEE. (h) IDS and the maximum surface temperature versus the coolant flow rate. (i) Integrated structure of GaN HEMT devices using microchannel and TSV. Reproduced with permission [94].

图15. (a) Design concept for microchannel heat transfer. (b) Infrared thermal imaging temperature readings at a VD of 10 V and a VG of 2 V. Remote cooling is shown on the left, while embedded cooling is displayed on the right. (c) Compared I–V characteristics. Reproduced with permission [41]. Copyright 2023, IEEE. (d) Schematic illustration of GaN HEMT with complicated microchannel cooling technique. (e) Visualization of fluid flow within the mMMC (monolithically integrated manifold microchannel) structure. (f) Total thermal resistance versus flow rate. (g) Benchmark comparison illustrates the COP against the maximum heat flux (q) for a 60 ◦C temperature rise. (h) Temperature related performance comparison. Reproduced with permission [38].

图16. (a) Schematic of the Ga2O3 SBD with double-side-cooling flipchip pac age. Waveforms of current and voltage for (b) bottom-cooled and (c) two-sided-cooled during the surge current experiment. (d) Simulated max junction temperature as a function of peak surge current in 10-ms surge tests. Reproduced with permission [104].

图17. (a) Schematic of the Ga2O3 MOSFET with diamond doubleside cooling. (b) Transient temperature rise under a power density of 4 W/mm. Reproduced with permission [105]. Copyright 2023, IEEE. (c) Schematic cross-sectional views of the buried-ohmic SBD with flipchip packaging. (d) Surge current characteristics of the buried-ohmic and recessed-anode SBDs with a stress duration of 1 ms. (e) Surge I–V loops of the different devices. Reproduced with permission [106].