2025Nature重磅综述,台积电怎么看3D-IC热管理材料?

来源 | Nature Reviews electrical engineering

链接 | https://doi.org/10.1038/s44287-025-00196-0

00

从“台积电视角”,看3D封装热管理材料的未来方向

在先进封装迅猛发展的当下,热管理材料正成为制约3D集成芯片性能的关键瓶颈之一。随着2.5D/3D封装技术不断推进,芯粒堆叠、功耗提升、热流密度增加,使得原有材料体系难以胜任高效散热的任务。对于材料企业而言,理解整条产业链下游的痛点和方向,是制定产品战略的基础。

前段时间,小编曾撰写过一篇关于台积电CoWoS封装热管理的文章,这种Chip-on-Wafer-on-Substrate(CoWoS)异构封装方案本质上就是对先进封装热挑战的正面回应。而台积电作为2.5D封装的顶尖厂商,如何看待“材料热瓶颈”这件事,是更值得我们关注和深入解读的。

AI芯片热到极限?CoWoS封装里藏着怎样的“散热”难题

最近,Nature Reviews Electrical Engineering发表了一篇重量级综述论文《Thermal management materials for 3D-stacked integrated circuits》。该文由台积电研发团队主笔,联合法布里(TSMC San Jose)和学术界(如东京大学、斯坦福大学)的专家共同完成,系统梳理了当前3D集成电路的热挑战、材料选择逻辑、界面工程问题、热特性测试方法及未来研究路线图。

在我看来,这不仅仅是一篇学术综述,更是台积电对于热管理材料路线的系统性表达,其中所传递的思考和判断,对材料企业具有极强的现实指导价值。它明确指出了材料导热性之外更重要的“可集成性”、强调了界面热阻(TBR)作为当前热瓶颈的核心地位,并系统分析了不同材料(如金刚石、AlN、SiC、BN等)在实际工艺流程中的优劣与限制。

接下来,小编将对这篇文章做一次详尽的拆解和翻译,试图厘清一些热管理材料的问题!

01

背景:先进封装带来的“热难题”,正从设计问题转变为材料瓶颈

随着AI、高性能计算(HPC)、大数据等对芯片算力的持续拉升,芯片架构正加速从平面走向立体,从系统走向异构。无论是堆叠逻辑芯片与高带宽内存的3D-IC,还是台积电主推的CoWoS与SoIC等2.5D封装方案,都在显著提升单位面积的计算密度与功能集成度。但与之相伴的,是一个日益严重却常被低估的问题:热,正在成为下一代芯片性能的决定性因素之一。

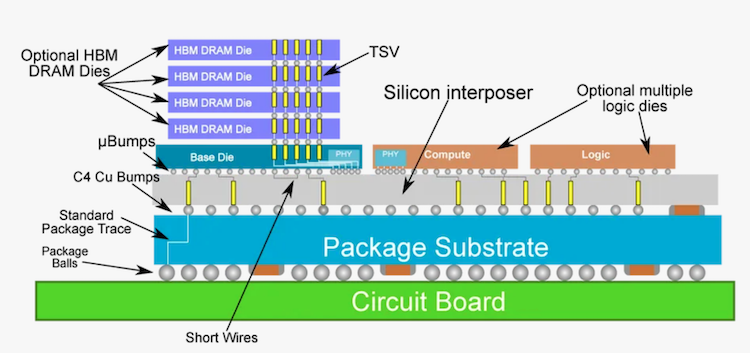

CoWoS结构(图源:科技前线阵地)

传统的平面CMOS器件,硅衬底本身就是很好的散热路径。然而,当芯片堆叠、功率密度升高、互联复杂化、热路径拉长,热量的排出就不再是一个“靠后处理”的问题,而是直接影响到器件性能、稳定性乃至寿命的核心挑战。

特别是近年来逐渐普及的背面供电(BSPDN)架构,进一步压缩了前端热路径,把多个低导热绝缘层(如SiO₂ bonding layer)引入系统,使得自热效应(self-heating)加剧,局部热点升温明显。据研究,相较传统供电路径,BSPDN器件的自热温度上升可达 30%以上。

与此同时,界面热阻(Thermal Boundary Resistance, TBR)成为热传导路径上的最大瓶颈之一。随着材料堆叠与异质集成的增加,一个芯片内部可能出现几十乃至上百个热阻界面,而每一个界面的热传导效率,都可能成为“致命短板”。

在这种背景下,传统“堆热导率高材料”的思路已逐渐失效。能否在满足热传导性能的同时,兼顾工艺兼容性、电绝缘性、机械稳定性,乃至大面积低温可加工性,成为评估材料价值的新标准。

02

一次关于极限散热能力的系统验证

近日,台积电的W.-Y. Woon 从材料、工艺、集成、测试四个层面,对3D集成中的热管理问题进行了系统梳理。在这篇综述中台积电团队系统回顾了当前适用于3D集成芯片的热管理材料体系,并指出:随着器件朝着纳米尺度和垂直堆叠发展,界面热阻(TBR)已成为限制热传导效率的核心瓶颈。针对这一问题,团队强调必须从材料本体导热性、界面声子匹配能力、热应力适配性及制造工艺兼容性多维度同时考量。文章列举了包括单晶/多晶金刚石、AlN、BN、SiC、BAs、石墨烯等多类材料的典型参数,如单晶金刚石的热导率可达1700–2400 W/m·K,界面TBR最低可降至1 m²·K/GW(Si/diamond),而传统AlN在低温沉积条件下也能保持~100 W/m·K的垂直导热率,TBR可控制在300 MW/m²·K范围内。尤其是在界面设计方面,文章指出通过引入如非晶SiC等“声子桥接层”可有效提升TBC,实现更低的界面温度梯度。此外,台积电还特别强调材料的“可加工性”与“工艺相容性”,如AlN可在400°C以下沉积、BN在低温下制备时需解决结晶度不足等问题;同时,综述也首次系统总结了热性能测试方法的选择路径,如3ω法适用于片上测试,TDTR适合亚微米多层膜栈的界面测量,为后续材料开发提供了标准化方向。这些成果不仅全面描绘了先进封装时代热管理材料所需具备的综合能力,也体现了台积电对材料导热机制与工艺集成之间耦合关系的深入理解,为材料研发端提供了清晰可落地的方向参考。研究成果以“Thermal management materials for 3D-stacked integrated circuits”为题发表在《Nature Reviews Electrical Engineering》期刊。

03

图文导读

图1. 器件架构和系统集成引发的散热问题。

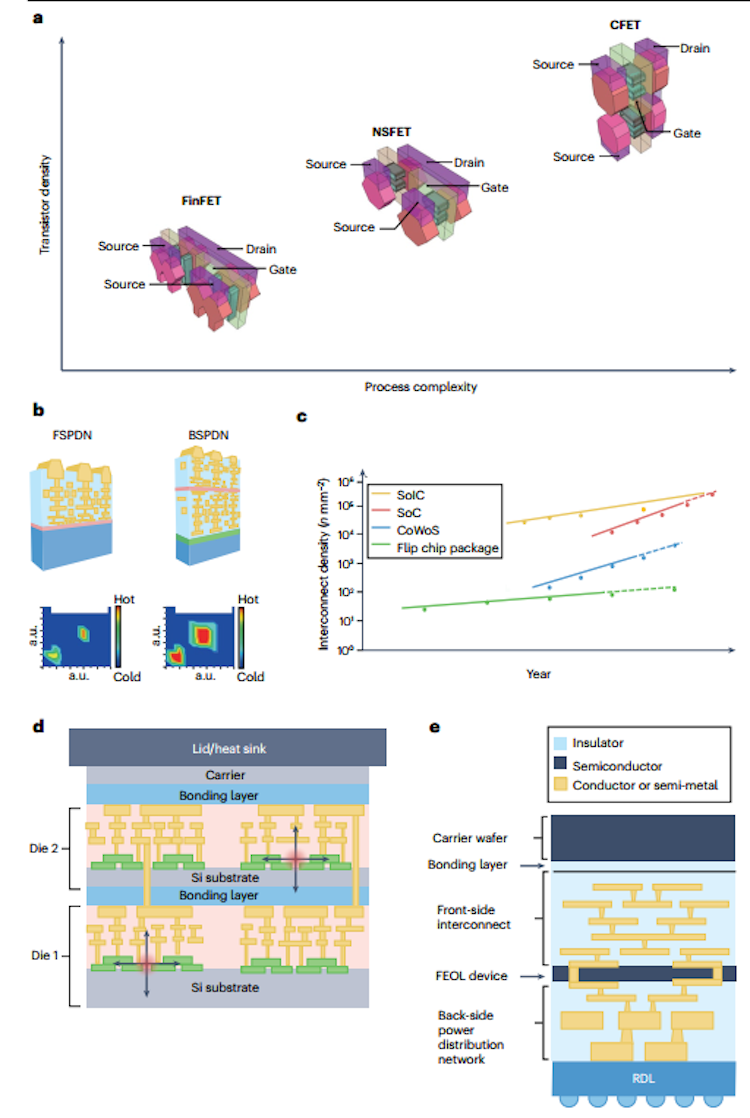

图1系统展示了当前主流器件架构和封装集成方式下的散热路径挑战。从FinFET进化至NSFET、CFET,器件本体的热路径变得更长更复杂。特别是在采用BSPDN(背面供电网络)架构后,热量需要穿越多层低导热层才能到达热沉,导致局部热点显著升温。同时,在系统层面,3D堆叠(如CoWoS、SoIC)进一步压缩了散热空间,使得每一个热界面都可能成为性能瓶颈。

表1列出了当前最具代表性的热管理材料的带隙、导热率以及已实现的最佳界面热阻(TBR)或热边界电导(TBC)。单晶金刚石和多晶金刚石以接近理论极限的导热率领跑,但其界面匹配性仍为挑战;AlN、SiC、BN等则在导热性和工艺兼容性之间提供更佳平衡。该表为材料厂商选材提供了量化参考。

表1. 热管理材料的热性能

图2. 热管理材料的集成挑战。

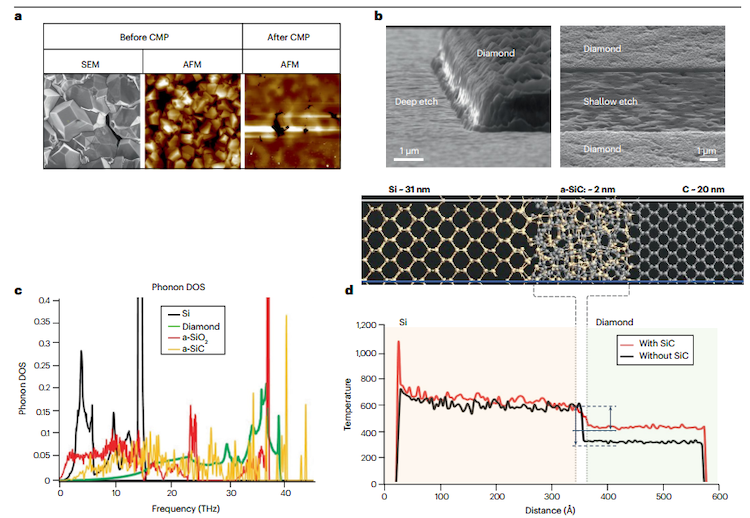

图2聚焦于材料集成过程中的几个技术难点:如金刚石的化学机械抛光后仍存在内含孔隙(a)、各类等离子刻蚀技术在图形定义上的表现(b)、界面声子失配带来的高热阻(c)、以及通过引入a-SiC中间层降低TBR的模拟结果(d)。这些细节揭示了高导热材料“难用”的真正原因。

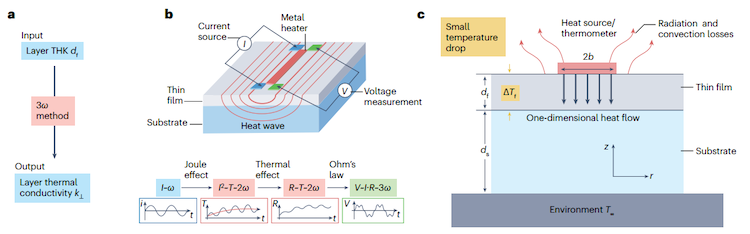

图3. 3ω法的工作原理。

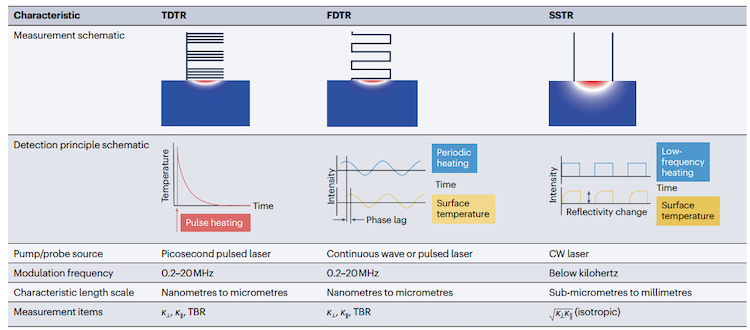

表2. 热反射法。

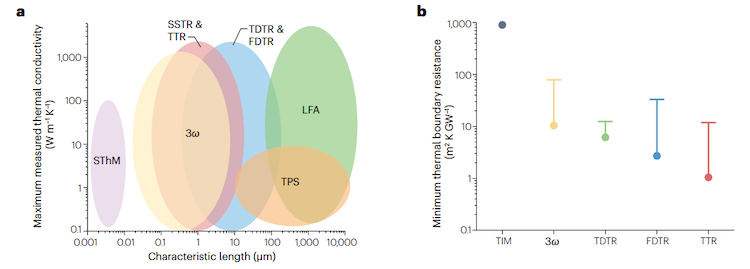

图4. 热表征技术的能力。

图4a展示了主流热导率测量方法在不同厚度材料中的应用范围;图4b则比较了各方法在TBR测量上的灵敏度下限。可以看出,TDTR和FDTR在亚微米薄膜和低TBR系统中表现出色,成为当前前沿研究中最常用的工具之一。图表清晰展现了“选对测试方法”对材料开发的重要性。