【深度】AI芯片热管理,微通道液冷产学研前沿合集

01

芯片是“AI时代的引擎”

2022年ChatGPT 的横空出世,让“生成式AI”从技术概念跃升为大众应用。作为OpenAI于2022年发布的自然语言大模型,ChatGPT仅用两个月就突破1亿月活,成为历史上增长最快的消费级应用。这一爆发式现象迅速引发全球科技企业对大模型的集体响应。

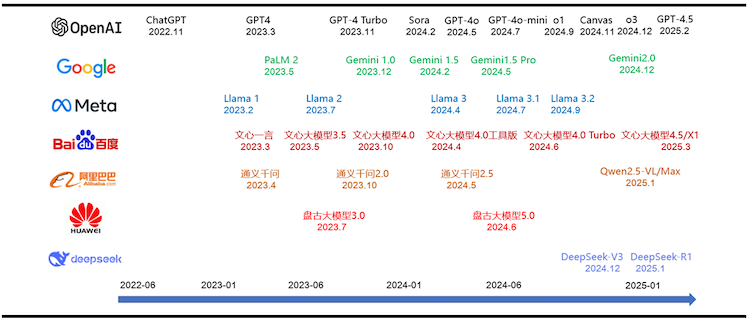

图1. 全球部分科技企业发布大模型产品情况。

谷歌、Meta、百度、阿里、华为、DeepSeek等公司陆续推出自研大模型,并不断迭代优化。2025年2月,OpenAI发布最新一代模型 GPT-4.5,集通用性、情绪智能和推理能力于一体,其在人类偏好评估中在创造性、专业性、实用性上全面超越前代。GPT-4.5的发布再次验证了“大模型即平台”的产业逻辑,也加速推动对底层算力基础设施的重塑。支撑这一切的,是AI芯片的持续进化。根据Epoch AI的数据,2012年至2023年间,用于训练大模型的算力总量增长近亿倍,AI芯片已经从专用ASIC/GPU向高热密度、高带宽的异构集成架构演进。

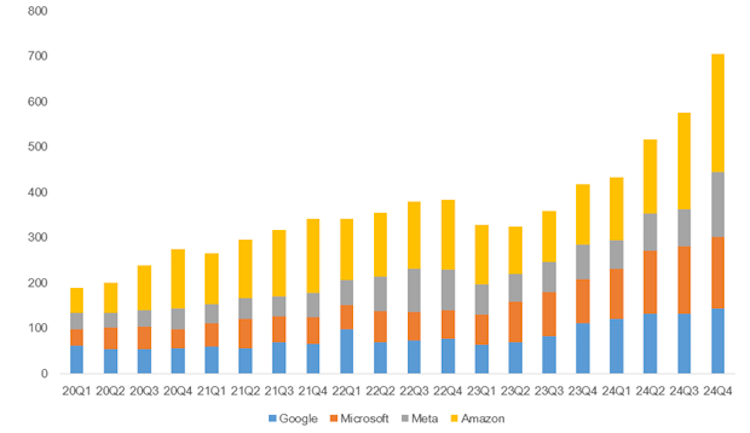

与此同时,AI正在改变全球科技产业的资本支出结构。2024年四季度,北美四大云厂商(微软、谷歌、Meta、亚马逊)的资本开支合计达706亿美元,同比增长69%。其中大部分流向AI基础设施部署,尤其是数据中心中的AI训练与推理芯片部署。

图2. 2020-2024年北美四大云厂商资本开支情况(亿美元)

2023年,人工智能AI芯片市场规模达到536亿美元;2024年,人工智能AI芯片市场规模达到712.5亿美元;2025年,人工智能AI芯片市场规模达到919.6亿美元。(来源:Gartner)

大模型在飞速演化,AI芯片正站在风口之巅。但与此同时,它也正面临一个日益严峻的问题:热。算力越强、封装越紧凑,单位面积上的热流密度就越高。从百瓦到千瓦级,AI芯片的热设计正逼近系统极限,也为热管理提出了全新的挑战。

02

芯片热了以后,我们是怎么“散”掉它的?

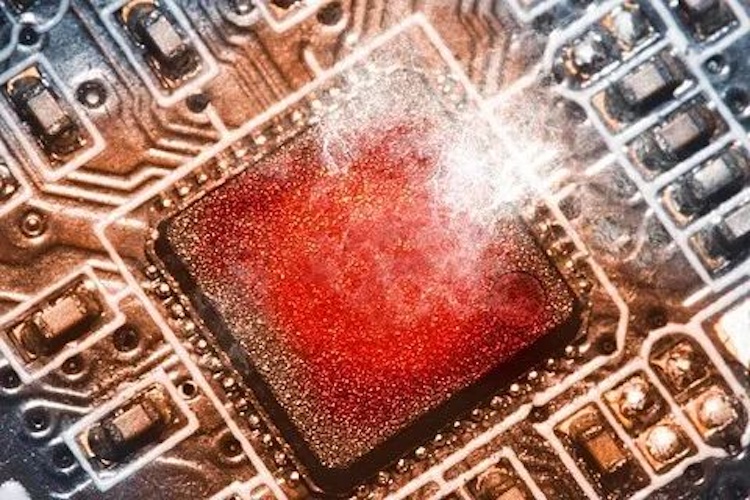

AI芯片的内部是将大量晶体管及其他元件集成在硅芯片表面的小面积区域内。随着摩尔定律的推进,晶体管数量呈指数增长,从数百个发展到如今每个芯片内含有数百亿个晶体管。与此同时,单位面积内的最大热通量已达到 200 W/cm²,并预计将很快突破 500 W/cm²,局部甚至可能超过 1000 W/cm²。热不仅是芯片性能的瓶颈,也是芯片可靠性的隐患。研究表明,当温度超过 70–80°C 时,电子器件的故障率将以近指数级上升;每升高 1°C,可靠性降低约 5%。据统计,超过 55% 的电子产品故障与温升直接相关,因此,如何高效进行芯片热管理,已成为芯片架构、封装和材料设计中的关键环节。

图1. 芯片发热示意图

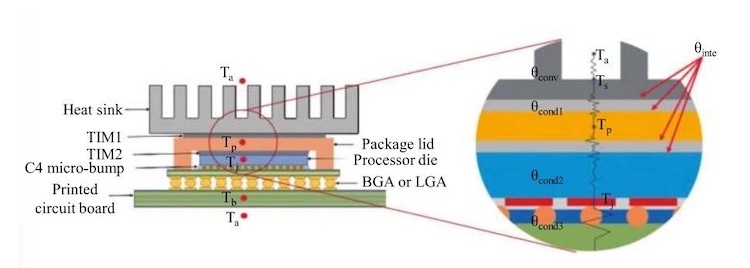

芯片热管理的核心在于:将核心区域产生的热量高效传递至环境中。图2所示为传统倒装封装结构中的热路径,散热过程主要依赖以下三种传热机制:热传导(Conduction):芯片内部、封装层和导热材料中热能的主要传递方式;对流(Convection):芯片外部热量向空气或液冷介质散发;热辐射(Radiation):在芯片中占比极小,通常忽略不计。

芯片热量从核心区域出发,经由焊点、基板、热界面材料(TIM)、封装盖板等路径,最终传递至散热器,再通过空气或液体流动将热带走。空气冷却的对流换热系数较低(约10–100 W/m²·K),通常需 100–1000°C 的温差才能传递出 1 W/cm² 的热流密度,因此在芯片顶部安装散热器、风扇等结构成为常见做法,以增加有效换热面积。

图2. 传统封装结构中芯片的散热路径。

当前随着集成电路制造工艺和功率密度的不断进步,芯片级热管理技术必须不断发展以满足散热要求。各种芯片冷却技术已经发展起来,包括风冷、冷板液冷、微通道冷却、浸入式冷却、热管冷却、射流冲击冷却、喷雾冷却、热电冷却等。随着液冷技术的崛起发展,微通道和浸入式冷却技术被广泛采用。

03

微通道液冷:芯片级散热的“新基准”

微通道液冷技术是在芯片或封装内部设计微米/纳米级流道,液体冷却介质直接流经这些微通道,极大提升热交换效率,实现高密度热流的快速带走。相比传统风冷、均热板散热,微通道液冷具有更高的传热系数和更低的温差。微通道散热能力可以通过表面对流传热系数、努塞尔数以及散热过程中单位面积能达到的最大热流密度和综合散热性能系数等来进行表征

图3. 芯片级微通道液冷。

传统的微通道热沉(traditional microchannel heat sink, TMC)在1981年被D. B. Tuckerman等首次提出。他们使用KOH腐蚀液在400 μm厚硅片的一 面刻蚀出了宽度和深度分别为50 μm和302 μm的矩形微通道,在另一面制作了薄膜式热电阻作为加热 源,以水作为冷却介质开展了实验研究,发现在 216 kPa压损下,芯片表面温升为71℃时,散热能力高达790W/cm2,散热能力超过了当时已知的冷却方式所能达到的水平。 而后学者们针对微通道的流动换热特性进行了大量研究。

图4. 各种微通道结构

M. I. Hasan 等研究了不同通道横截面形状(如圆形、方形、矩形、等 三角形和梯形)对其性能的影响,结果表明增加通道数量可以提高传热系数但压降也会急剧增加。 同时,流体在传统的平直微通道内沿流动方向逐渐吸热升温,流动与热边界层不断发展,换热能力恶化,导致流动末端壁面温度急剧升高,温度均匀性较差。 由于液体相变可以充分利用工质的汽化潜热而不使芯片温度升高太多,因此国内外团队对微通道热沉的流动沸腾特性也进行大量的研究。

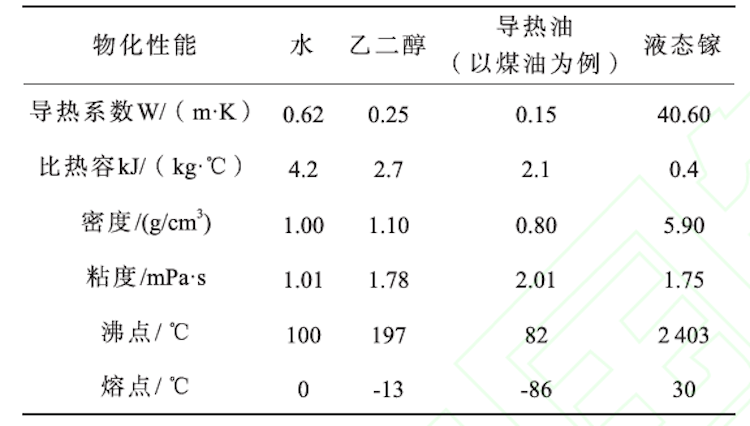

表1. 常压30℃ 时传统冷却介质的物理参数对比

微通道结构对微通道散热器的传热和传质过程都有极大的影响。对微通道结构进行设计和优化需要考虑其拓扑结构、截面形状/尺寸及层数等多方面的特征进行综合优化。除微通道结构外,通道内采用何种流体作为冷却介质也会对微流道热沉的散热能力产生很大的影响,目前,微通道热沉冷却介质主要采用空气、液态水乙二醇以及液态金属等。由表1可知,30℃下水的导热系数为 0.62W/(mK)高于乙二醇和导热油,更高于空气。它成本低,液态高纯水性质稳定,粘度低,具有较好的导热和流动性能,是最常用的微通道冷却介质。

与传统散热技术相比,不论是散热能力还是集成发展,微通道散热结构均有着较强的优势。对微通道结构进行优化设计是提高微通道散热结构综合散热性能的主要手段。其中,嵌入式分层歧管微通道结构体现出较高的散热潜力。

04

代表性科研进展综述

4.1 早期近芯片冷却技术

2006年,IBM COLGAN等提出交错条状翅片结合歧管的近芯片冷却方案,实现了对大尺寸单芯片的高功率密度散热。2021年,中国科学院微电子所CHEN等提出歧管-硅-窄缝协同设计方案(如图5所示),实现流体均匀分布的近芯片冷却。

图5. 近芯片冷却冷板结构

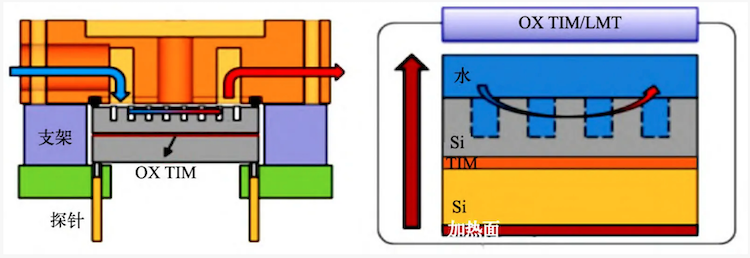

2021年,台积电WU等提出两种近芯片冷却方案:氧硅键合和液态金属界面材料,分别达到高功率密度散热且控制温升,结构如图6所示。

图6. 2种近芯片冷却方案

第一种方案是在芯片与硅微通道之间采用氧硅键合进行集成,针对面积为 540 mm2的芯片,该方案可以在 83℃温升下,实现总功耗为 2.3 kW、平均热流密度为 426 W/cm2 的有效冷却。第二种方案是将界面材料换成液态金属,可以在 75℃的温升下,满足总功耗为1.8 kW、平均热流密度为 333 W/cm2 的芯片散热需求。

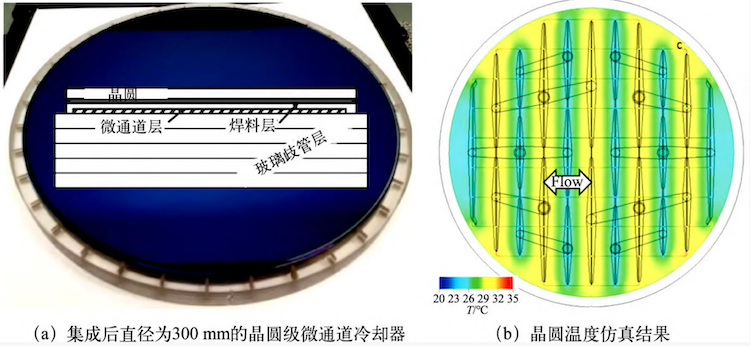

4.2 晶圆级微通道冷却

2023年,IBM 的 COLGAN 等开发了一种直径为 300 mm的晶圆级系统歧管式微通道冷却方案,硅晶圆冷却结构如图7所示。该方案使用 SnPb 焊料将交错式翅片微通道冷却结构与热测试晶圆键合在一起,对于总功耗为 14 kW的晶圆,核心热点区域的最大温升小于 18℃。这项工作可以为未来超大尺寸、大功耗晶圆级集成的冷却提供参考。

图7 硅晶圆冷却结构

4.3 芯片内嵌冷却技术

芯片内嵌冷却大幅降低热阻,是高性能芯片热管理的前沿方向。1981年,Stanford TUCKERMAN和PEASE提出最早的硅衬底微通道结构,控制高热流密度下芯片温升。2017年,佐治亚理工学院的 SARVEY 等研究了针对 400 mm2 FPGA 的芯片内嵌冷却方案,其结构如图8所示,当芯片的功耗为 32 W时,最大温升仅为 4℃

图8 针对 FPGA的芯片内嵌冷却结构

2021年,台积电的 WU 等在 VLSI 会议上发表了一项芯片内嵌冷却的技术,针对高性能芯片,直接在芯片背面刻蚀微通道,可以在温升为 65℃的情况下,实现对 481 W/cm2 热流密度的冷却,相比于采用氧硅键合和液态金属的近芯片冷却方案,芯片内嵌冷却方案的热阻更低。

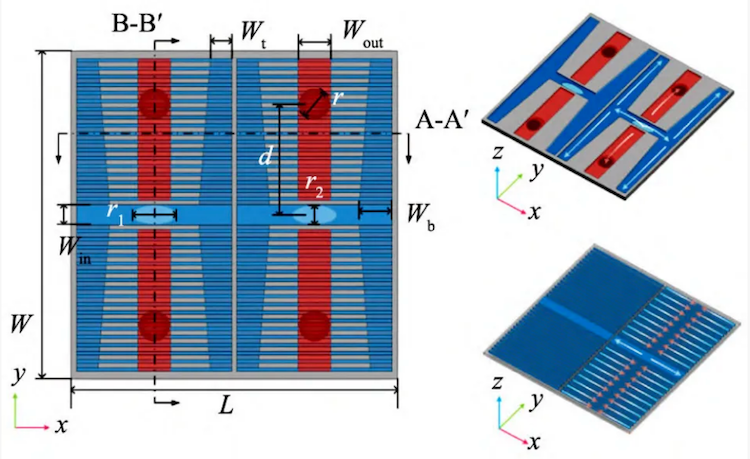

2022 年,北京大学的 YANG等提出了一种双 H型芯片歧管内嵌冷却结构,采用硅-硅键合工艺集成,其结构如图9所示。针对面积为400 mm2、功耗为 417 W 的芯片,在温升为 22.2℃的情况下,实现了对 104.3 W/cm2 热流密度的冷却。

图9 双H型芯片歧管内嵌冷却结构

4.4 微射流冷却技术

2019年,Stanford JUNG提出嵌入式歧管微射流冷却,针对小面积芯片实现高效冷却。在 0.1 L/min 的流率下,该结构针对面积为 25 mm2、热功耗为 62.5 W 的芯片,可实现对 250 W/cm2 热流密度的有效冷却,将温升控制在90℃以内。

2019年,比利时微电子中心WEI等通过3D打印多喷嘴阵列,实现高效局部热点冷却如图10所示。在0.6 L/min的流速下,该结构实现了对功耗为 50 W、热流密度为 78 W/cm2、面积为 64 mm2 的芯片的冷却,芯片的最大温升被控制在 15℃左右,系统热阻可降至0.25 K/W,在外部泵功耗为 0.4 W的条件下,可以获得62500 W/(m2·K)的换热系数。

图10 阵列射流冷却结构

4.5 微通道两相冷却技术

微通道单相冷却适用于500 W/cm²以下热流密度,超过则需两相冷却提升。2017年,IBM CHAINER等提出微针肋放射状微通道相变冷却,针对2000 W/cm²热点实现温升约65℃。

图11 嵌入式相变冷却结构

2017年,Stanford PALKO等利用金刚石和烧结铜球相变换热微槽,冷却局部热点高达5kW/cm²。

图12 基于高导热金刚石和表面烧结铜球的相变换热微槽结构

2018年,普渡DRUMMOND提出分层歧管式微通道,实现910 W/cm²冷却。

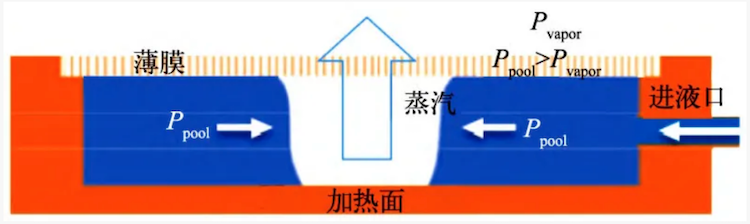

2017-2020年,佛罗里达大学FAZELI及ALIPANAH等开展薄液膜沸腾换热研究,实现超高临界热流密度冷却。

图13. 薄液膜沸腾换热结构

在微通道中引入相变冷却可以大幅度提高冷却能力,但是由于通道内部的相变情况很难控制,在高热流密度冷却过程中会出现超过临界热流密度导致的换热失稳等问题,例如相分离不完全,系统接近干涸极限等,最终会导致芯片烧毁。此外,对于工质的选择,需要考虑使用的压力与沸点范围,将系统内部各处压力控制在合理范围内,使得换热位置处的冷却工质始终处于气液两相状态。

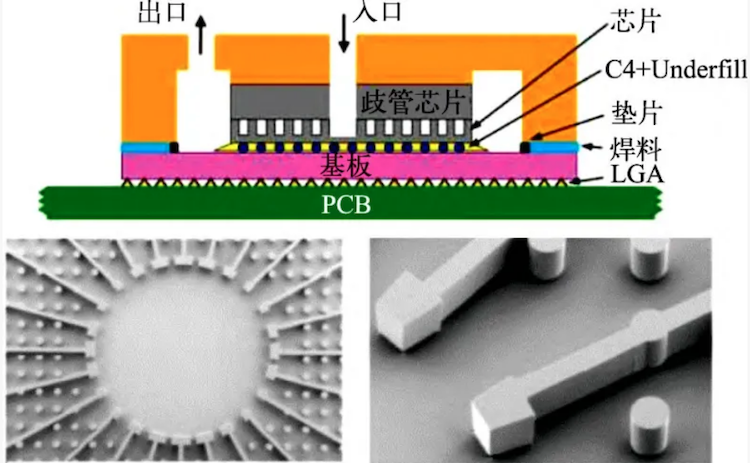

2020 年瑞士洛桑联邦理工学院(EPFL)在《Nature》发表了一篇题为《Co-designing electronics with microfluidics for more sustainable cooling》的论文,首次将“电子器件设计”与“微流体冷却”紧密融合,提出将冷却结构直接嵌入芯片硅片本体的“共设计”理念(Co-design)。

图14. 文章信息

这项研究试图解决的是一个长期存在的热管理瓶颈:热源与冷却通道之间的距离过远,即使冷却技术本身再先进,在跨越封装界面、热界面材料(TIM)、热沉等多重热阻后,最终仍会因热阻积累导致效率大幅下降。

EPFL 团队的思路是颠覆性的——直接在芯片本体(硅片)内刻蚀出微流体通道,让冷却液第一时间接触发热源,从源头上减少热阻。这种结构不仅需要高度的三维微制造工艺(包括深硅刻蚀、键合、绝缘层处理),也需要将冷却系统的压力、流量与芯片封装过程无缝集成。

图15. 成果表征

05

代表性的产业化动态进展

(1)台积电ECT2025最新技术披露:芯片直接液冷

ECTC 2025台积电展示了CoWos-R最新的热管理的研究进展,主要讨论了两部分内容:(1)对比了三种不同的TIM1在CoWos-R的热管理性能;(2)介绍了一种名为硅集成微冷却器(IMEC-Si)的液冷架构。

在本研究中采用三种先进 TIM 的 CoWoS-R 热测试载体(TTV),包括:(1)石墨薄膜 TIM;(2)液态金属凝胶 TIM;(3)铟金属 TIM。为进一步提升金属 TIM封装的热性能,设计了具备冲击结构的新型液冷系统,以应对超过 2000W 的热功率输入。tsmc该方案利用先进的硅制造技术,在有源硅芯片的背面直接制造硅微柱阵列,以实现直接液体冷却。他们研究了微柱的几何形状和流动条件,并成功证明:使用 40°C 的水作为冷却剂,IMC-Si能够在接近全晶圆尺寸的芯片上耗散2000瓦的均匀热量,且系统能耗极低,小于 10 瓦。

图16. 集成液体歧管以实现直接液体冷却的 CoWoS-R 封装示意图(图源:IEEE ECTC)

为了展示 IMC- Si与台积电用于高性能计算(HPC)应用的 3D Fabric™平台的集成能力,该解决方案被集成到 3.3 倍晶圆尺寸的 CoWoS-R热测试载体(TTV)平台上。已开发出一种 CoWoS组装工艺,通过应用密封剂来实现液体入口/出口歧管的组装。针对组装流程中不同温度导致的CoWoS- R封装翘曲变化,对密封剂的机械可靠性进行了测试。同时,还在严苛的压力条件下对密封剂进行测试,以确保无泄漏。台积电还证明在允许结温(Tj)上升 60°C(合理流量下晶圆入口温度为 20°C)的情况下,IMC-Si可实现超过 3000 瓦的散热能力。

(2)Corintis:硅芯片内微流体冷却系统的产业化先锋

瑞士工程科技公司Corintis成立于2022年,专注于为高性能芯片开发微流体自冷却系统。公司源自瑞士洛桑联邦理工学院(EPFL)与欧洲核子研究组织(CERN)的合作,由Remco van Erp、Sam Harrison和Elison Matioli教授联合创立。

图17.创始人

Corintis将硅微流体冷却通道无缝集成到芯片中,使液体冷却剂直接与硅芯片接触,大幅提升散热效率。其核心技术是一体化的3D微通道网络,通道尺寸仅数十微米,并与芯片热点精确对齐,实现散热速率提升10倍、冷却性能提高50倍。

图18.结构示意图

为降低液体输送能耗,Corintis设计了类似人体血液循环的网络结构,仅在热点区域设窄通道,显著减少泵送能量。该技术支持高达2000 W/cm²的散热,适用于高功率密度和垂直集成芯片,是下一代芯片热管理的关键。

商业上,Corintis与芯片制造商及大型数据中心合作,提供微流体冷却系统设计和制造服务。公司还开发了Glacierware云平台,能自动根据芯片热图定制微通道设计,计划推广到更多行业。2022年8月,Corintis获得1500万瑞士法郎投资,致力于加速试点项目并完善Glacierware平台,推动可持续高性能计算的发展。

(3)JetCool——将实验室理念推向工程化的代表企业

JetCool 是美国马萨诸塞州的创新冷却企业,成立之初即以“打破传统冷却范式”为目标,其研发路径与EPFL提出的芯片微通道冷却有着高度的技术理念共振。但不同的是,JetCool 所采用的微喷射冷却阵列,则更像是从系统端优化的“软着陆”版本——实现了类似的热阻极限突破,但更容易嵌入到现有产业链之中。

JetCool的核心理念是微尺度喷射冷却(Microconvective Cooling)。其冷却模块由密布微喷嘴的金属板构成,这些喷嘴以几十微米的尺寸,能够将冷却液以高速精准喷射至芯片表面最热区域,随后迅速带走热量。

图19. 产品示意图

该技术诞生于麻省理工学院林肯实验室,为数据中心服务器和高性能计算设备提供具有低耗能、高性能和减少碳排放的散热需求。JetCool 的核心结构是一块含有多个微喷孔(Microjet)的散热面板,通过极小直径(通常为 50–100 μm)的喷孔,以极高速度将冷却液直接“喷射”到处理器表面关键热区,液体随后沿表面径向扩散、换热并排出。

图20. 散热结构示意图

其结构特点包括:

局部强化换热:热斑处冷却液对流系数可高达 100,000 W/(m²·K);

低热阻设计:测试中接触热阻可低至 0.09 K/W;

分区喷射结构:可根据芯片热分布自定义喷孔密度与布局;

无需相变:采用单相液冷,避免了相变控制复杂性;

对芯片侵入性低:无须更改芯片封装结构,可贴合裸芯片或标准封装底面使用

05

结语

在AI芯片持续突破算力极限的今天,热管理技术早已从边缘配角跃升为核心瓶颈和技术竞赛的前线。微通道冷却、内嵌液冷、两相流控等一系列创新方案,不仅回应了极端热流密度的挑战,更重新定义了高性能计算的结构设计边界。正如我们本次热管理大会所强调的那样,散热技术的未来不再只是“辅助”系统,而是推动芯片架构演进与算力可持续扩展的决定性力量。

回顾全球科研与产业的协同进展,从Corintis等初创公司到IBM、台积电的前沿实验,再到学术界的大胆探索,我们正站在一个微尺度热管理技术飞跃的前夜。这不仅是挑战,更是一次前所未有的工程机遇。

作为2025第六届热管理大会的组织方,我们希望通过搭建跨界交流的平台,汇聚产业与学术的智慧,共同推动AI芯片热管理技术迈入更高维度的创新周期。未来,我们将继续关注技术融合、材料突破、系统集成等关键领域的发展,助力构建面向智能计算时代的高效散热生态。

参考资料[1] 将微流体冷却系统无缝集成到硅芯片中,瑞士工程科技公司Corintis将芯片冷却效能提高50倍 | 瑞士创新100强,钛媒体;

[2] 用于高密度集成微系统的微通道散热技术研究进展,《微电子学与计算机》;

[3] 歧管微通道热沉研究进展与展望,《微通道换热专栏》;

[4] 基于内嵌式微通道芯片散热结构设计研究综述,《集成电路与嵌入式系统》;

[5] Comprehensive review and future prospects on chip-scale thermal management: Core of data center’s thermal management,《Applied Thermal Engineering》;

[6] 高算力Chiplet的热管理技术研究进展,《电子与封装》;